# **DSP56300 Family Manual**

## 24-Bit Digital Signal Processor

DSP56300FM/AD Revision 2.0, August 1999

OnCE<sup>™</sup> and Mfax are trademarks of Motorola, Inc. Intel<sup>"</sup> is a registered trademark of the Intel Corporation. All other trademarks are those of their respective owners.

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not authorized for use as components in life support devices or systems intended for surgical implant into the body or intended to support or sustain life. Buyer agrees to notify Motorola of any such intended end use whereupon Motorola shall determine availability and suitability of its product or products for the use intended. Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Employment Opportunity /Affirmative Action Employer.

How to reach us:

### USA/Europe/Locations Not Listed:

Motorola Literature Distribution P.O. Box 5405 Denver, Colorado 80217 1 (800) 441-2447 1 (303) 675-2140

### Motorola Fax Back System (Mfax<sup>™</sup>):

TOUCHTONE (602) 244-6609 1 (800) 774-1848 RMFAX0@email.sps.mot.com

### Asia/Pacific:

Motorola Semiconductors H.K. Ltd. 8B Tai Ping Industrial Park 51 Ting Kok Road Tai Po, N.T., Hong Kong 852-26629298

### **Technical Resource Center:**

1 (800) 521-6274

DSP Helpline dsphelp@dsp.sps.mot.com

### Japan:

Nippon Motorola Ltd SPD, Strategic Planning Office141 4-32-1, Nishi-Gotanda Shinagawa-ku, Japan 81-3-5487-8488

Internet: http://www.motorola-dsp.com/

© MOTOROLA INC., 1999

## Contents

### Chapter **1** Introduction

| 1.1   | Core Overview                                 |

|-------|-----------------------------------------------|

| 1.1.1 | Data Arithmetic Logic Unit (Data ALU) 1-2     |

| 1.1.2 | Address Generation Unit (AGU) 1-3             |

| 1.2   | Program Control Unit (PCU) 1-4                |

| 1.3   | On-chip Instruction Cache Controller 1-5      |

| 1.4   | Port A External Memory Interface 1-6          |

| 1.5   | Phase Lock Loop (PLL) and Clock Generator 1-6 |

| 1.6   | Hardware Debugging Support 1-7                |

| 1.7   | Direct Memory Access (DMA) 1-7                |

| 1.8   | Introduction to Digital Signal Processing 1-8 |

| 1.9   | Summary of Features 1-11                      |

| 1.10  | Manual Organization                           |

### Chapter 2 Core Architecture Overview

| 2.1     | Core Buses                                             |

|---------|--------------------------------------------------------|

| 2.2     | Core Processing                                        |

|         | Processing States                                      |

| 2.3.1   | Normal Processing State                                |

| 2.3.2   | Exception Processing State (Interrupt Processing)      |

| 2.3.2.1 | Hardware Interrupt Source                              |

| 2.3.2.2 | Software Interrupt Sources                             |

| 2.3.2.3 | Interrupt Priority Structure                           |

| 2.3.2.4 | Instructions Preceding the Interrupt Instruction Fetch |

| 2.3.2.5 | Interrupt Types         2-13                           |

| 2.3.2.6 | Interrupt Arbitration                                  |

| 2.3.2.7 | Interrupt Instruction Fetch 2-14                       |

| 2.3.2.8 | Interrupt Instruction Execution                        |

| 2.3.3   | Reset Processing State                                 |

| 2.3.4   | Wait Processing State    2-17                          |

| 2.3.5   | Stop Processing State                                  |

| 2.3.6   | Debug State                                            |

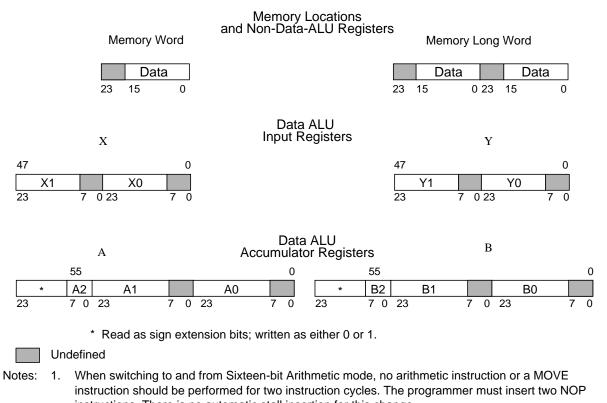

### Chapter <mark>3</mark> Data Arithmetic Logic Unit

| 3.1     | Introduction                                            |

|---------|---------------------------------------------------------|

| 3.2     | Data ALU Architecture                                   |

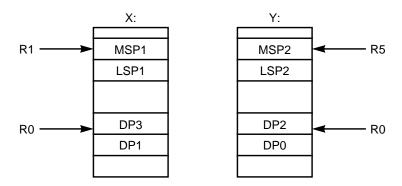

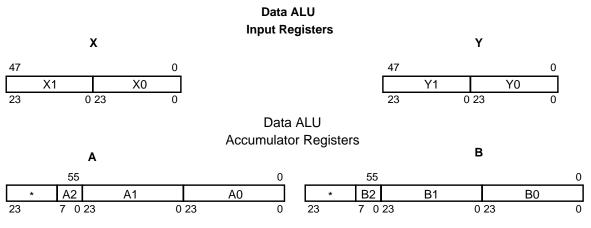

|         | Data ALU Input Registers (X1, X0, Y1, Y0)               |

|         | Multiplier-Accumulator (MAC) Unit                       |

| 3.2.3   | Data ALU Accumulator Registers (A2, A1, A0, B2, B1, B0) |

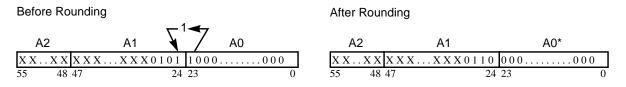

| 3.2.4   | Accumulator Shifter                                     |

| 3.2.5   | Bit Field Unit (BFU)                                    |

| 3.2.6   | Data Shifter/Limiter                                    |

| 3.2.6.1 | Scaling                                                 |

| 3.2.6.2 | Limiting                                                |

| 3.3     | Data ALU Arithmetic and Rounding                        |

| 3.3.1   | Data Representation                                     |

| 3.3.2   | Rounding Modes                                          |

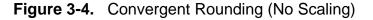

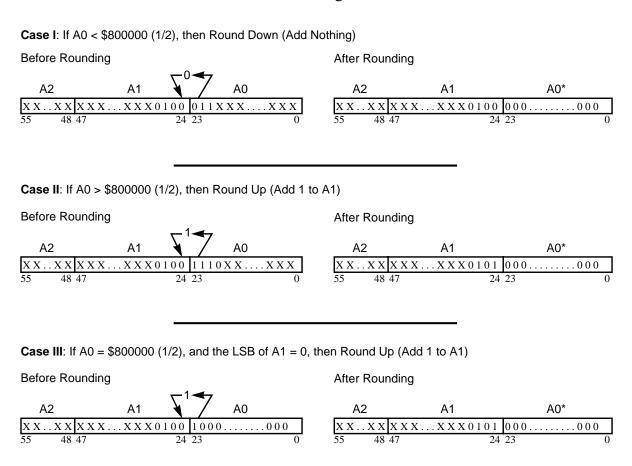

| 3.3.2.1 | Convergent Rounding 3-8                                 |

| 3.3.2.2 | Twos-Complement Rounding 3-10                           |

| 3.3.3   | Arithmetic Saturation Mode 3-11                         |

| 3.3.4   | Multiprecision Arithmetic Support                       |

| 3.3.4.1 | Double-Precision Multiply Mode                          |

| 3.3.5   | Block Floating-Point FFT Support 3-14                   |

| 3.4     | Data ALU Programming Model    3-15                      |

| 3.5     | Sixteen-Bit Arithmetic Mode 3-15                        |

| 3.5.1   | Moves in Sixteen-Bit Arithmetic Mode 3-16               |

| 3.5.1.1 | Moves into Registers or Accumulators 3-16               |

| 3.5.1.2 | Moves from Registers or Accumulators 3-17               |

| 3.5.1.3 | Short Immediate moves 3-19                              |

| 3.5.1.4 | Scaling and Limiting 3-19                               |

| 3.5.2   | Sixteen-bit Arithmetic 3-19                             |

| 3.6     | Pipeline Conflicts                                      |

| 3.6.1   | Arithmetic Stall                                        |

| 3.6.2   | Status Stall                                            |

| 3.6.2.1 | Transfer Stall                                          |

|         |                                                         |

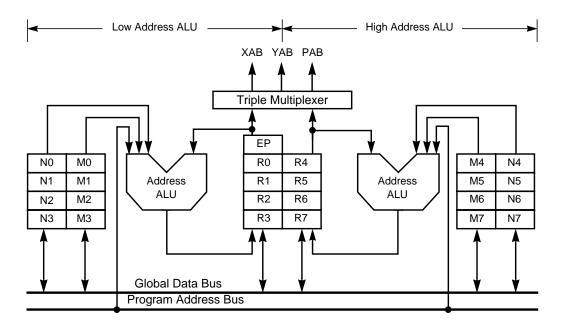

### Chapter 4 Address Generation Unit

| 4.1 | AGU Architecture               | 4-1 |

|-----|--------------------------------|-----|

| 4.2 | Sixteen-bit Compatibility Mode | 4-3 |

| 4.3 | Programming Model              | 4-4 |

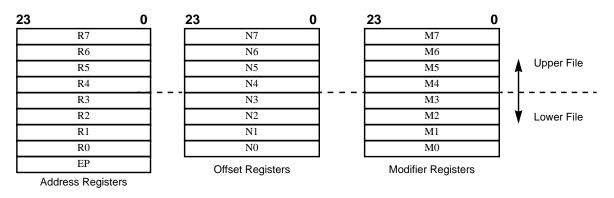

| 4.3.1 | Address Register Files 4-4                 |

|-------|--------------------------------------------|

| 4.3.2 | Stack Extension Pointer 4-5                |

| 4.3.3 | Offset Register Files 4-5                  |

| 4.3.4 | Modifier Register Files 4-6                |

| 4.4   | Addressing Modes 4-6                       |

| 4.4.1 | Register Direct Modes 4-7                  |

| 4.4.2 | Address Register Indirect Modes 4-7        |

| 4.4.3 | PC-relative Modes 4-9                      |

| 4.4.4 | Special Address Modes 4-9                  |

| 4.5   | Address Modifier Types 4-10                |

| 4.5.1 | Linear Modifier (Mn = \$XXFFFF)            |

| 4.5.2 | Reverse-Carry Modifier ( $Mn = $ \$000000) |

| 4.5.3 | Modulo Modifier ( $Mn = Modulus - 1$ )     |

| 4.5.4 | Multiple Wrap-Around Modulo Modifier 4-13  |

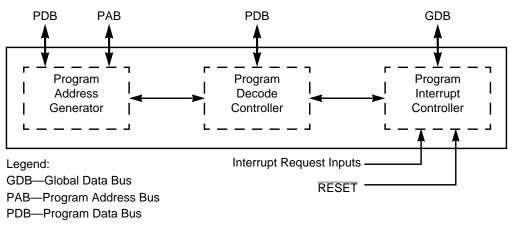

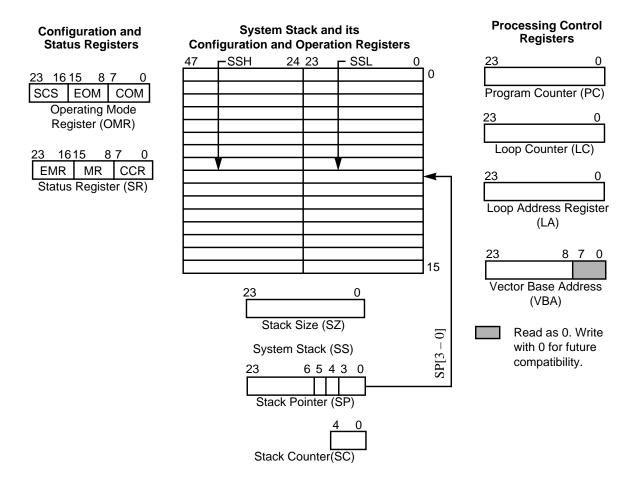

### Chapter <mark>5</mark> Program Control Unit

| Overview                                           | 5-1                       |

|----------------------------------------------------|---------------------------|

| PCU Hardware Architecture                          | 5-3                       |

| Instruction Pipeline                               | 5-3                       |

| Programming Model                                  | 5-4                       |

| Configuration and Status Registers                 | 5-5                       |

| Operating Mode Register                            | 5-6                       |

| 2 Status Register (SR)                             | 5-11                      |

| Stack and Stack Extension                          | 5-18                      |

| System Stack Configuration and Operation Registers | 5-18                      |

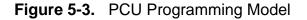

| Stack Pointer (SP) Register                        | 5-20                      |

| 2 Stack Counter (SC) Register                      | 5-22                      |

| 3 Stack Size (SZ) Register                         | 5-22                      |

| Program, Loop, and Exception Processing Control    | 5-23                      |

| Program Counter (PC) Register                      | 5-23                      |

| 2 Loop Address (LA) Register                       | 5-23                      |

| B Loop Counter (LC) Register                       | 5-23                      |

| Vector Base Address (VBA) Register                 | 5-23                      |

|                                                    | PCU Hardware Architecture |

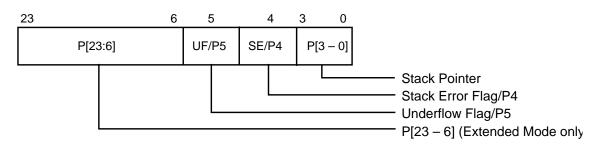

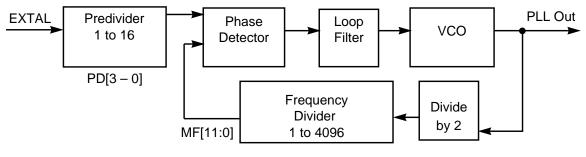

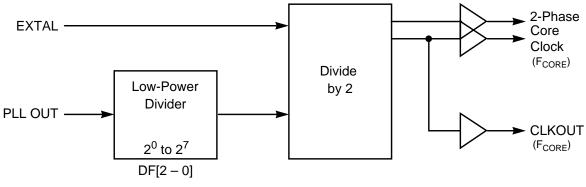

### Chapter 6 PLL and Clock Generator

| 6.1 | PLL and Clock Signals | 6-2 |

|-----|-----------------------|-----|

| 6.2 | PLL Block             | 6-2 |

| 6.2.1     | Frequency Predivider                           |

|-----------|------------------------------------------------|

| 6.2.2     | Phase Detector and Charge Pump Loop Filter 6-3 |

| 6.2.3     | Voltage Controlled Oscillator (VCO)            |

| 6.2.3.1   | Divide by 2                                    |

| 6.2.3.2   | Frequency Divider                              |

| 6.2.3.3   | PLL Control Elements 6-4                       |

| 6.2.3.3.  | Clock Input Division 6-4                       |

| 6.2.3.3.2 | 2 Frequency Multiplication 6-4                 |

| 6.2.3.3.  | 3 Skew Elimination 6-4                         |

| 6.2.3.3.4 | 4 Clock Generator                              |

| 6.2.3.3.  | 5 Low-Power Divider (LPD)                      |

| 6.2.3.3.  | 5 Internal and External Clock Pulse Generator  |

| 6.2.3.3.2 | 7 Operating Frequency 6-6                      |

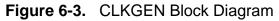

| 6.3 F     | LL Programming Model 6-6                       |

| 6.4 C     | Clock Synchronization                          |

| 6.5 I     | Design Guidelines for Ripple and PCAP 6-10     |

### Chapter **7** Debugging Support

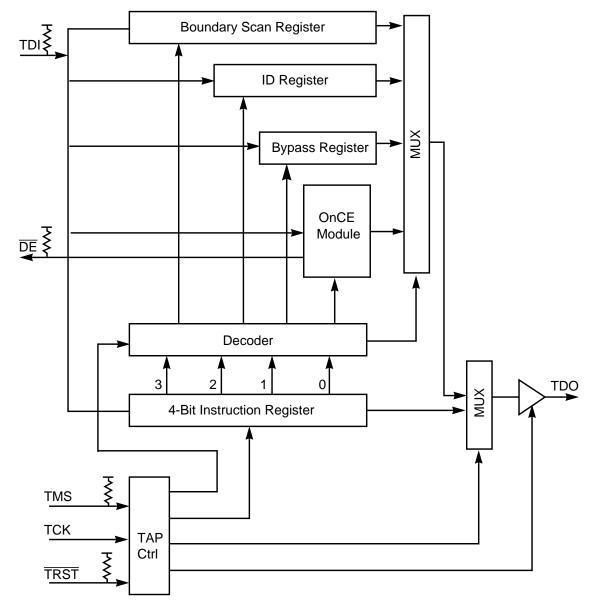

| 7.1 J   | ГАG Test Access Port 7-2                |

|---------|-----------------------------------------|

| 7.1.1   | Boundary Scan Architecture Overview     |

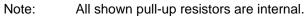

| 7.1.2   | TAP Controller         7-3              |

| 7.1.3   | Boundary Scan Register                  |

| 7.1.4   | Instruction Register                    |

| 7.1.4.1 | EXTEST $(B[3-0] = 0000) \dots 7-7$      |

| 7.1.4.2 | SAMPLE/PRELOAD (B[3 – 0] = 0001)7-7     |

| 7.1.4.3 | IDCODE $(B[3-0] = 0010) \dots 7-7$      |

| 7.1.4.4 | CLAMP $(B[3-0] = 0011)$                 |

| 7.1.4.5 | HI-Z (B[ $3 - 0$ ] = 0100)              |

| 7.1.4.6 | ENABLE_ONCE(B[3:0] = 0110) 7-9          |

| 7.1.4.7 | DEBUG_REQUEST(B[3 - 0] = 0111) 7-9      |

| 7.1.4.8 | BYPASS $(B[3-0] = 1111) \dots 7-10$     |

| 7.1.5   | DSP56300 JTAG Restrictions              |

| 7.2 C   | DnCE' Module                            |

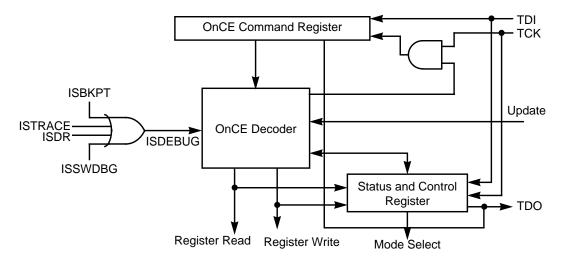

| 7.2.1   | OnCE Controller                         |

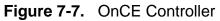

| 7.2.1.1 | OnCE Command Register (OCR) 7-13        |

| 7.2.1.2 | OnCE Decoder (ODEC)                     |

| 7.2.1.3 | OnCE Status and Control Register (OSCR) |

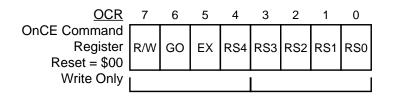

| 7.2.2   | OnCE Memory Breakpoint Logic            |

| 7.2.2.1 | OnCE Memory Address Latch (OMAL) 7-18   |

| 7.2.2.2 | OnCE Memory Limit Register 0 (OMLR0)                             |

|---------|------------------------------------------------------------------|

| 7.2.2.3 | OnCE Memory Address Comparator 0 (OMAC0)                         |

| 7.2.2.4 | OnCE Memory Limit Register 1 (OMLR1)                             |

| 7.2.2.5 | OnCE Memory Address Comparator 1 (OMAC1)                         |

| 7.2.2.6 | OnCE Breakpoint Control Register (OBCR)                          |

| 7.2.2.7 | OnCE Memory Breakpoint Counter (OMBC)                            |

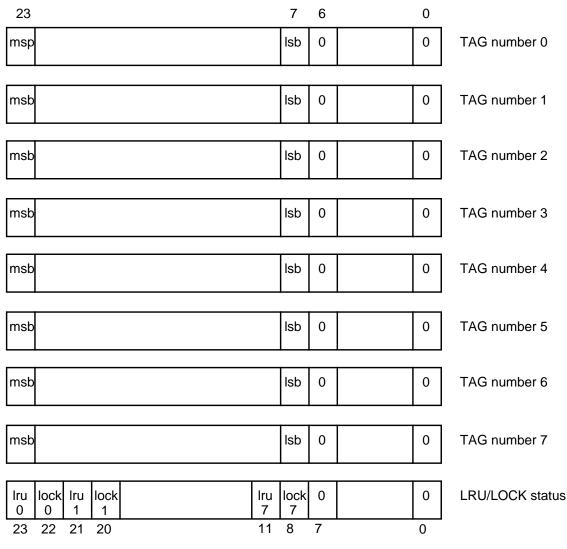

| 7.2.3   | Cache Support                                                    |

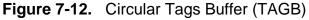

| 7.2.3.1 | OnCE Trace Logic                                                 |

| 7.2.4   | Methods of Entering Debug Mode                                   |

| 7.2.5   | Trace Buffer                                                     |

| 7.2.6   | OnCE Commands and Serial Protocol                                |

| 7.2.7   | OnCE Module Examples                                             |

| 7.2.7.1 | Checking Whether the Chip Has Entered Debug Mode                 |

| 7.2.7.2 | Polling the JTAG Instruction Register                            |

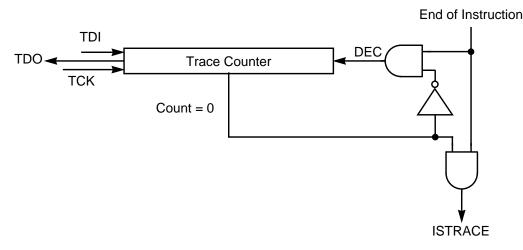

| 7.2.7.3 | Saving Pipeline Information                                      |

| 7.2.7.4 | Reading the Trace Buffer                                         |

| 7.2.7.5 | Displaying a Specified Register                                  |

| 7.2.7.6 | Displaying X Memory Area Starting at Address \$xxxxxx            |

| 7.2.7.7 | Returning From Debug Mode to Normal Mode to Current Program 7-32 |

| 7.2.7.8 | Returning from Debug Mode to Normal Mode to a New Program 7-32   |

| 7.3 Ex  | camples of JTAG-OnCE Interaction                                 |

| 7.3.1   | Address Trace Mode                                               |

### Chapter 8 Instruction Cache

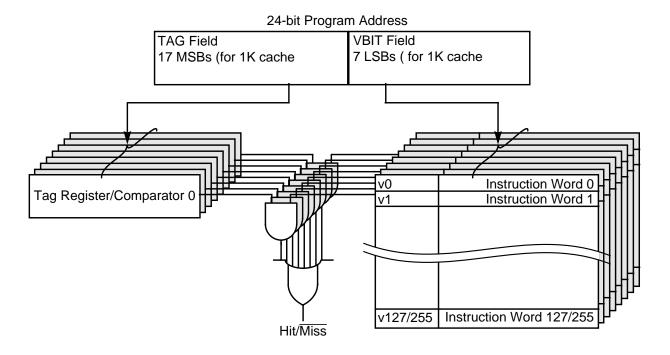

| 3.1    Instruction Cache Architecture               | 8-2 |

|-----------------------------------------------------|-----|

| 3.2 Cache Programming Model                         | 8-3 |

| 3.2.1 Cache Operation                               | 8-4 |

| B.2.1.1         Program Fetch                       | 8-4 |

| 3.2.1.2 Cache Hit                                   | 8-4 |

| 3.2.1.3 Cache Word Miss When Burst Mode Is Disabled | 8-4 |

| 3.2.1.4 Cache Word Miss When Burst Mode Is Enabled  | 8-5 |

| 3.2.1.5 Sector Miss                                 | 8-5 |

| B.2.2Default Mode After Hardware Reset              | 8-6 |

| 3.3 Cache Locking                                   | 8-6 |

| 3.4 Cache Unlocking                                 | 8-6 |

| 3.5 Flushing the Cache.                             | 8-7 |

| B.6 Data Transfers to/from Instruction Cache        | 8-8 |

| B.6.1   DMA Transfers                               | 8-8 |

| 3.6.2Software-Controlled Transfers                  | 8-8 |

| 8.7 | Using the Instruction Cache in Real-Time Applications | 8-9  |

|-----|-------------------------------------------------------|------|

| 8.8 | Debugging Instruction Cache Operation                 | 8-10 |

### Chapter <mark>9</mark> External Memory Interface (Port A)

| 9.1     | Signal Description                                    | 9-2  |

|---------|-------------------------------------------------------|------|

| 9.2     | Port Operation                                        | 9-5  |

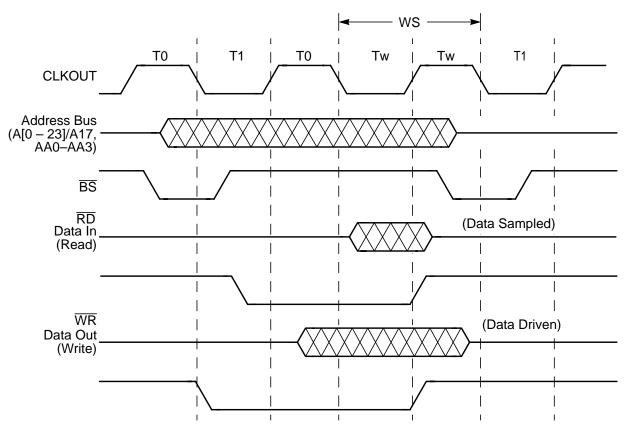

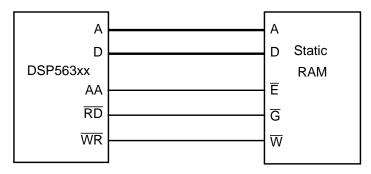

| 9.2.1   | SRAM Support                                          | 9-5  |

| 9.2.2   | DRAM Support                                          | 9-7  |

| 9.2.2.1 | DRAM In-Page Access                                   | 9-10 |

| 9.2.2.2 | DRAM Out-of-Page Access.                              | 9-10 |

| 9.3     | Port A Disable                                        | 9-11 |

| 9.4     | Bus Handshake and Arbitration.                        | 9-11 |

| 9.5     | Bus Arbitration Signals                               | 9-11 |

| 9.5.1   | The Arbitration Protocol.                             | 9-12 |

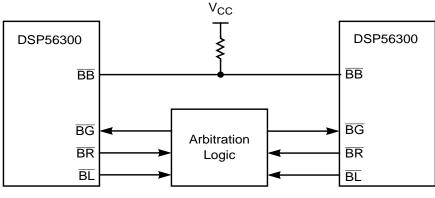

| 9.5.2   | Arbitration Scheme                                    | 9-13 |

| 9.5.3   | Bus Arbitration Example Cases                         | 9-14 |

| 9.5.3.1 | Case 1—Normal                                         | 9-14 |

| 9.5.3.2 | Case 2—Bus Busy                                       | 9-14 |

| 9.5.3.3 | Case 3—Low Priority                                   | 9-14 |

| 9.5.3.4 | Case 4—Default                                        | 9-14 |

| 9.5.3.5 | Case 5—Bus Lock during Read-Modify-Write Instructions | 9-14 |

| 9.5.3.6 | Case 6—Bus Parking                                    | 9-15 |

| 9.6     | Port A Control                                        | 9-15 |

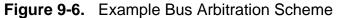

| 9.6.1   | Address Attribute Registers (AAR0–AAR3)               | 9-15 |

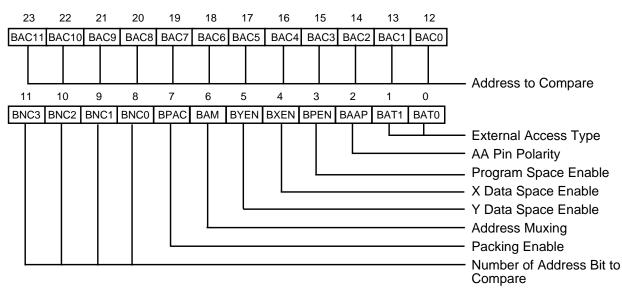

| 9.6.2   | Bus Control Register.                                 | 9-18 |

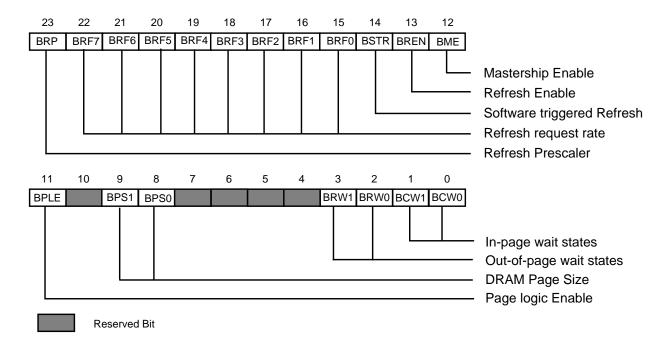

| 9.6.3   | DRAM Control Register                                 | 9-21 |

### Chapter 10 DMA Controller

| 10.1   | DMA Operational Overview                    | 10-3 |

|--------|---------------------------------------------|------|

| 10.1.1 | Basic Address Modes                         | 10-3 |

| 10.1.2 | Special Address Modes                       | 10-4 |

| 10.1.3 | Unmatched Source and Destination Dimensions | 10-4 |

| 10.1.4 | DMA Triggers (Request Sources)              | 10-5 |

| 10.1.5 | Transfer Mode                               | 10-5 |

| 10.2   | Timing (Core Clock Cycles)                  | 10-6 |

| 10.2.1 | Non-Overlap Between DMA Channels            | 10-6 |

| 10.2.2 | Overlap between DMA Channel and Core        | 10-7 |

| 10.3 Channel Priority 10-7                                       |

|------------------------------------------------------------------|

| 10.3.1 Priority Between DMA Channels 10-7                        |

| 10.3.2 Priority Between a DMA Channel and the Core 10-8          |

| 10.4 Special Uses of DMA With the Bus Interface Unit             |

| 10.4.1 Byte Packing 10-9                                         |

| 10.4.1.1 DRAM In-Page Accesses using DMA 10-9                    |

| 10.4.1.2 End-of-Block-Transfer Interrupt 10-9                    |

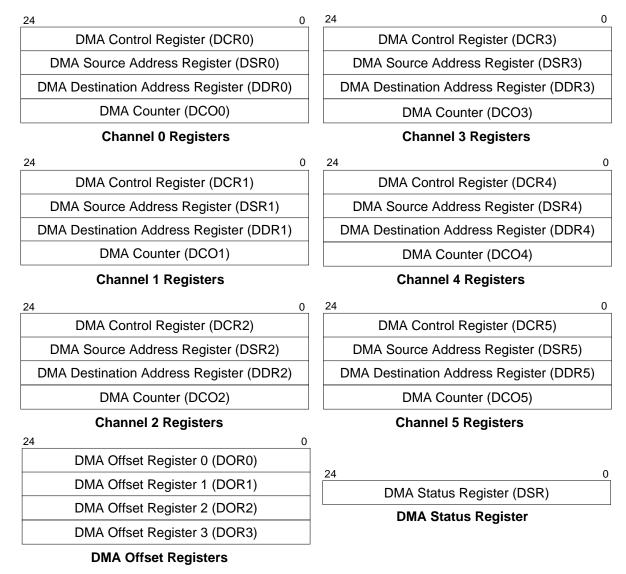

| 10.5 DMA Controller Programming Model 10-10                      |

| 10.5.1 DMA Source Address Registers (DSR0–DSR5) 10-10            |

| 10.5.2 DMA Destination Address Registers (DDR[5-0]) 10-11        |

| 10.5.3 DMA Counters (DCO[5 – 0]) 10-11                           |

| 10.5.3.1 DMA Counter Mode A—Single Counter 10-11                 |

| 10.5.3.2 DMA Counter Mode B—Dual Counter 10-12                   |

| 10.5.3.3 Circular Buffer (Length Less Than or Equal to 4K) 10-13 |

| 10.5.3.3.1 DMA Counter Modes C, D and E—Triple Counter 10-13     |

| 10.5.3.4 Circular Buffer (Length Greater Than 4K) 10-15          |

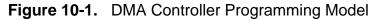

| 10.5.3.5 DMA Control Registers (DCR[5-0]) 10-16                  |

| 10.5.3.5.1 Non-3D Addressing Modes (D3D = 0) 10-21               |

| 10.5.3.5.2 3D Modes (D3D = 1) 10-22                              |

| 10.5.3.6 DMA Offset Registers (DOR[3-0]) 10-24                   |

| 10.5.3.7 DMA Status Register (DSTR) 10-24                        |

| 10.6 DMA Restrictions 10-26                                      |

# Chapter **11** Operating Modes and Memory Spaces

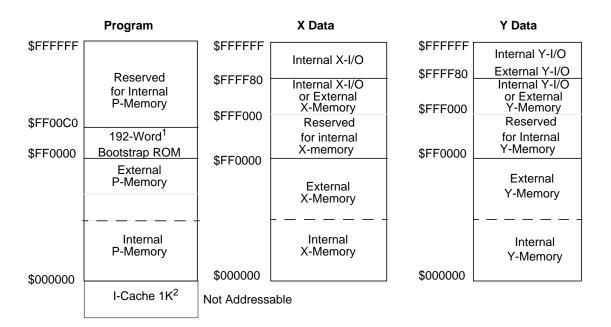

| 11.1 D   | SP56300 Family Core Memory Map 11               | 1-2 |

|----------|-------------------------------------------------|-----|

| 11.1.1   | X Data Memory Space 11                          | 1-3 |

| 11.1.2   | Internal X I/O Space 11                         | 1-3 |

| 11.1.3   | Switchable Internal or External X I/O Memory 11 | 1-5 |

| 11.1.3.1 | Reserved Space for X ROM or RAM 11              | 1-5 |

| 11.1.3.2 | External X Data Memory 11                       | 1-5 |

| 11.1.3.3 | Internal X Memory 11                            | 1-5 |

| 11.1.4   | Y Data Memory Space 11                          |     |

| 11.1.4.1 | Internal/External Y I/O Space 11                | 1-6 |

| 11.1.4.2 | Switchable Internal or External Y I/O Memory    | 1-6 |

| 11.1.4.3 | Reserved Space for Y ROM or RAM 11              | 1-6 |

| 11.1.4.4 | External Y Data Memory 11                       | 1-6 |

| 11.1.4.5 | Internal Y Memory                               | 1-6 |

| 11.1.5   | Program Memory                                  |     |

| 11.1.5.1 | Bootstrap ROM Space 11                          |     |

| 11.1.5.2 | Reserved Space for Program ROM 11-7 |

|----------|-------------------------------------|

| 11.1.5.3 | External Program Memory 11-7        |

| 11.1.5.4 | Internal Program Memory 11-7        |

| 11.1.5.5 | Internal Instruction Cache RAM 11-8 |

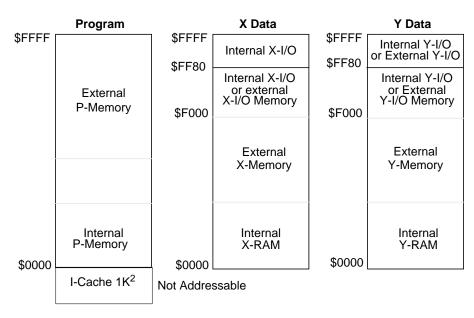

| 11.2 S   | ixteen-Bit Compatibility Mode 11-8  |

| 11.3     | Memory Switch Mode 11-9             |

### Chapter 12 Guide to the Instruction Set

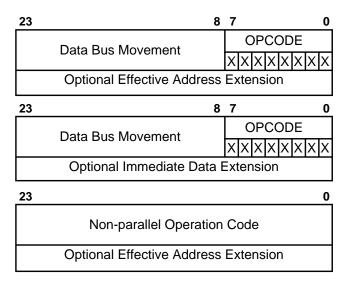

| 12.1   | Instruction Formats and Syntax 12-1                     |

|--------|---------------------------------------------------------|

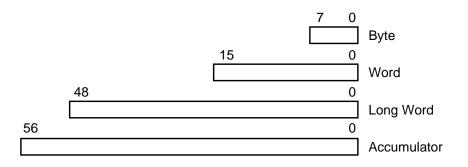

| 12.2   | Operand Lengths 12-3                                    |

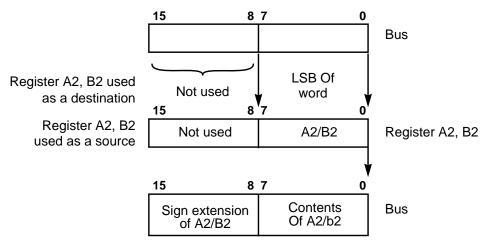

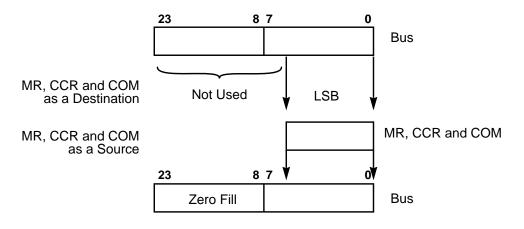

| 12.2.1 | Data ALU Registers 12-4                                 |

| 12.2.2 | AGU Registers 12-5                                      |

| 12.2.3 | Program Control Registers 12-5                          |

| 12.2.4 | Data Organization in Memory 12-6                        |

| 12.3   | Instruction Groups                                      |

| 12.3.1 | Arithmetic Instructions 12-7                            |

| 12.3.2 | Logical Instructions 12-9                               |

| 12.3.3 | Bit Manipulation Instructions                           |

| 12.3.4 | Loop Instructions                                       |

| 12.3.5 | Move Instructions                                       |

| 12.3.6 | Program Control Instructions 12-12                      |

| 12.4   | Guide to Instruction Descriptions 12-13                 |

| 12.4.1 | Notation                                                |

| 12.4.2 | Condition Code Computation                              |

| 12.5   | Instruction Partial Encoding 12-22                      |

| 12.5.1 | Partial Encodings for Use in Instruction Encoding 12-22 |

| 12.5.2 | Parallel Instruction Encoding of the Operation Code     |

| 12.5.2 | 1 Multiply Instruction Encoding 12-29                   |

| 12.5.2 | 2 Non-Multiply Instruction Encoding 12-30               |

### Chapter 13 Instruction Set

### Appendix A Instruction Timing and Restrictions

| A.1   | Overview                    | A-1  |

|-------|-----------------------------|------|

| A.2   | Instruction Sequence Delays | A-10 |

| A.2.1 | External Bus Wait States    | A-10 |

| A.2.2   | Instruction Fetch Delays                       |

|---------|------------------------------------------------|

| A.2.3   | Data ALU Interlock                             |

| A.2.4   | Address Register Interlocks                    |

| A.2.5   | Stack Extension Delays                         |

| A.2.6   | Program Flow Control Delays                    |

| A.2.6.1 | JMP to LA or to LA – 1                         |

| A.2.6.2 | RTI to LA or to LA – 1                         |

| A.2.6.3 | Conditional Instructions                       |

| A.2.6.4 | Interrupt Abort                                |

| A.2.6.5 | Degenerated DO loopA-16                        |

| A.2.6.6 | Annulled REP and DOA-16                        |

| A.3 In  | struction Sequence Restrictions A-16           |

| A.3.1   | Restrictions Near the End of DO Loops          |

| A.3.2   | General DO Restrictions                        |

| A.3.3   | ENDDO Restrictions                             |

| A.3.4   | BRKcc Restrictions                             |

| A.3.5   | RTI and RTS Restrictions                       |

| A.3.6   | SR Manipulation Restrictions                   |

| A.3.7   | SP/SC and SSH/SSL Manipulation Restrictions    |

| A.3.8   | Fast Interrupt RoutinesA-25                    |

| A.3.9   | REP Restrictions                               |

| A.3.10  | Stack Extension Restrictions                   |

| A.3.11  | Stack Extension Enable Restrictions            |

| A.4 Pe  | eripheral Pipeline Restrictions A-27           |

| A.4.1   | Polling a Peripheral Device for Write          |

| A.4.2   | Writing to a Read-Only Register                |

| A.4.3   | XY Memory Data Move                            |

| A.5 Si  | xteen-Bit Compatibility Mode Restrictions A-28 |

### Appendix <mark>B</mark> Benchmark Programs

| Benchmarks                                             |                                                                                                                                                                                          |                                                                                                                                                                                          |                                                                                                                                                                                          | B-2                                                                                                                                                                                                      |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real Multiply                                          |                                                                                                                                                                                          |                                                                                                                                                                                          |                                                                                                                                                                                          | B-3                                                                                                                                                                                                      |

| N Real Multiplies                                      |                                                                                                                                                                                          |                                                                                                                                                                                          |                                                                                                                                                                                          | B-4                                                                                                                                                                                                      |

| Real Update                                            |                                                                                                                                                                                          |                                                                                                                                                                                          |                                                                                                                                                                                          | B-5                                                                                                                                                                                                      |

| N Real Updates                                         |                                                                                                                                                                                          | ••                                                                                                                                                                                       |                                                                                                                                                                                          | B-6                                                                                                                                                                                                      |

| Real Correlation or Convolution (FIR Filter)           |                                                                                                                                                                                          | ••                                                                                                                                                                                       |                                                                                                                                                                                          | B-7                                                                                                                                                                                                      |

| Real * Complex Correlation or Convolution (FIR Filter) |                                                                                                                                                                                          | ••                                                                                                                                                                                       |                                                                                                                                                                                          | B-8                                                                                                                                                                                                      |

| Complex Multiply                                       |                                                                                                                                                                                          | ••                                                                                                                                                                                       |                                                                                                                                                                                          | B-10                                                                                                                                                                                                     |

| N Complex Multiplies                                   |                                                                                                                                                                                          | ••                                                                                                                                                                                       | ••                                                                                                                                                                                       | B-11                                                                                                                                                                                                     |

|                                                        | Real MultiplyN Real MultipliesReal Update.N Real UpdatesN Real UpdatesReal Correlation or Convolution (FIR Filter)Real * Complex Correlation or Convolution (FIR Filter)Complex Multiply | Real MultiplyN Real MultipliesReal Update.N Real UpdatesN Real UpdatesReal Correlation or Convolution (FIR Filter)Real * Complex Correlation or Convolution (FIR Filter)Complex Multiply | Real MultiplyN Real MultipliesReal Update.N Real UpdatesN Real UpdatesReal Correlation or Convolution (FIR Filter)Real * Complex Correlation or Convolution (FIR Filter)Complex Multiply | BenchmarksReal MultiplyN Real MultipliesReal Update.N Real UpdatesReal Correlation or Convolution (FIR Filter)Real * Complex Correlation or Convolution (FIR Filter)Complex MultiplyN Complex Multiplies |

| B.1.9  | Complex Update                                       |

|--------|------------------------------------------------------|

| B.1.10 | N Complex Updates                                    |

| B.1.11 | Complex Correlation or Convolution (FIR Filter) B-15 |

| B.1.12 | Nth Order Power Series (Real)B-17                    |

| B.1.13 | Second Order Real Biquad IIR Filter B-18             |

| B.1.14 | N Cascaded Real Biquad IIR Filter B-19               |

| B.1.15 | N Radix-2 FFT Butterflies (DIT, In-Place Algorithm)  |

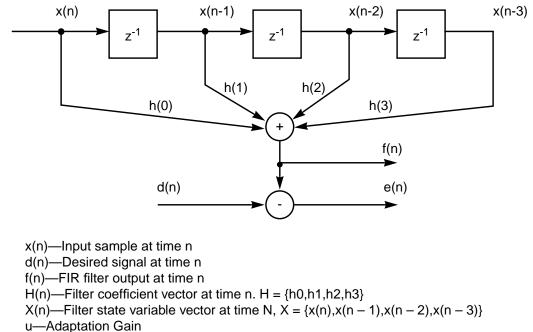

| B.1.16 | True (Exact) LMS Adaptive Filter B-21                |

| B.1.17 | Delayed LMS Adaptive FilterB-24                      |

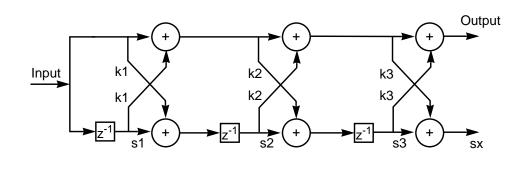

| B.1.18 | FIR Lattice Filter                                   |

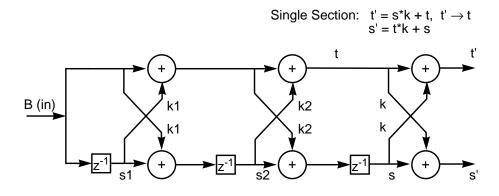

| B.1.19 | All Pole IIR Lattice Filter                          |

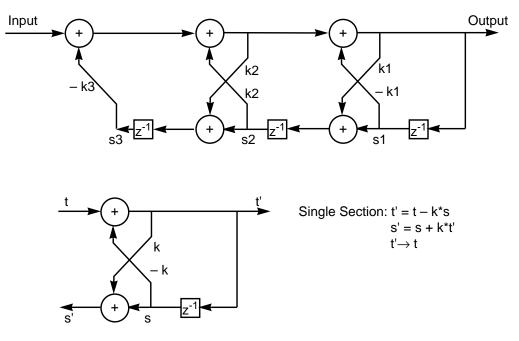

| B.1.20 | General Lattice Filter                               |

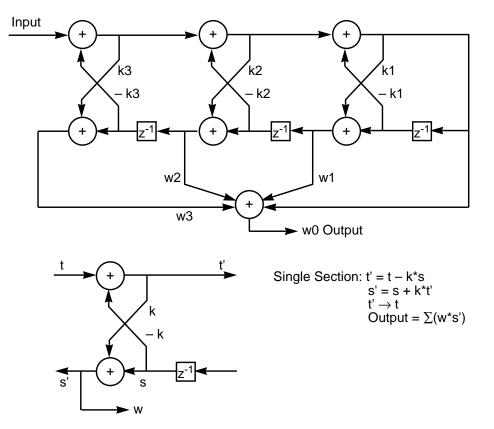

| B.1.21 | Normalized Lattice Filter                            |

| B.1.22 | [1 × 3][3 × 3] Matrix MultiplicationB-34             |

| B.1.23 | N Point 3 × 3 2-D FIR Convolution                    |

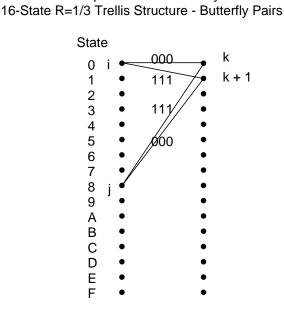

| B.1.24 | Viterbi Add-Compare-Select (ACS)B-38                 |

| B.1.25 | Parsing a Data Stream                                |

| B.1.26 | Creating a Data StreamB-42                           |

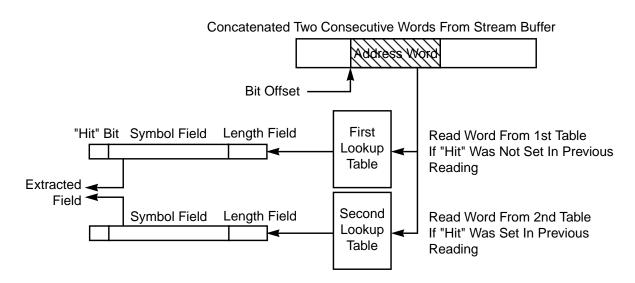

| B.1.27 | Parsing a Hoffman Code Data Stream B-45              |

# Appendix C From CDR Process to HiP Process

| C.1 | Voltage             | C-2 |

|-----|---------------------|-----|

| C.2 | Operating Frequency | C-2 |

| C.3 | Port A Timings      | C-2 |

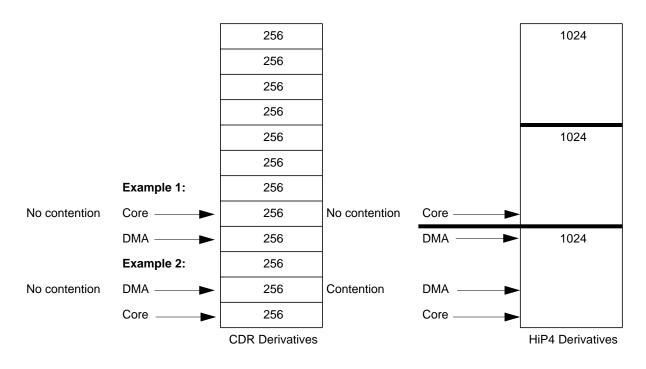

| C.4 | Memory Block Size   | C-3 |

# Figures

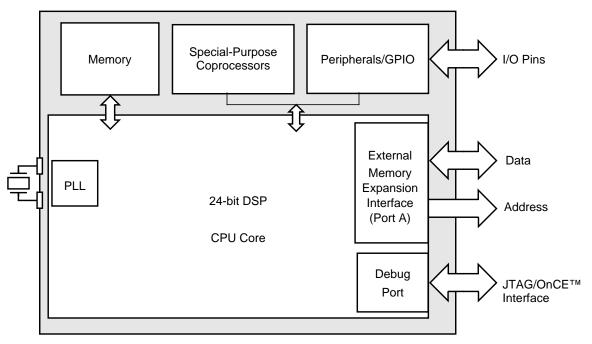

| Figure 1-1.  | DSP56300 Family-Based DSP Chip 1-1              |

|--------------|-------------------------------------------------|

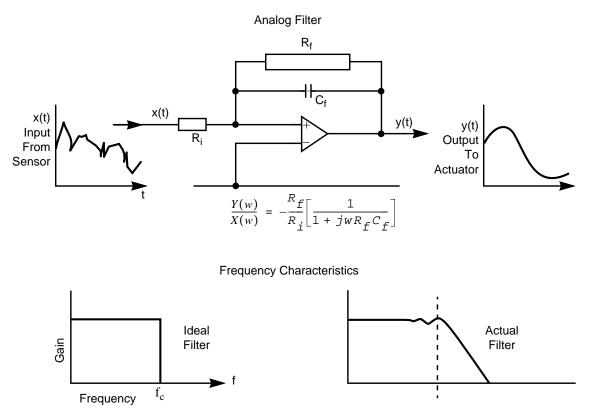

| Figure 1-2.  | Analog Signal Processing 1-8                    |

| Figure 1-3.  | Digital Signal Processing1-9                    |

| Figure 1-4.  | Mapping DSP Algorithms into Hardware1-11        |

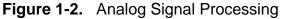

| Figure 2-1.  | DSP56303 Block Diagram                          |

| Figure 2-1.  | Interrupt Priority Register C (IPRC) 2-10       |

| Figure 2-2.  | Interrupt Priority Register P (IPRP) 2-11       |

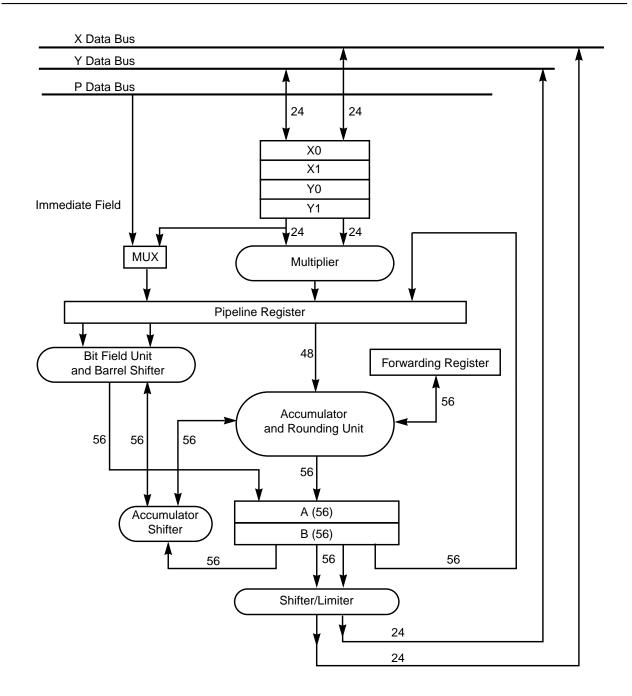

| Figure 3-1.  | Data ALU Block Diagram                          |

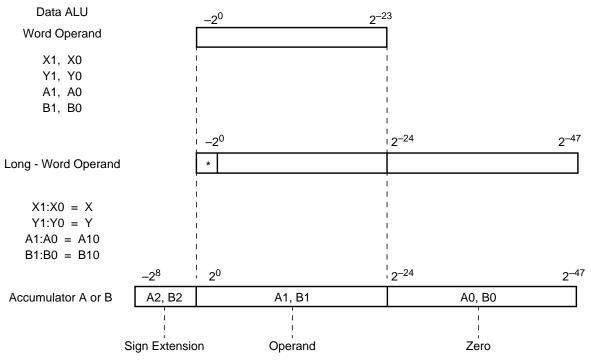

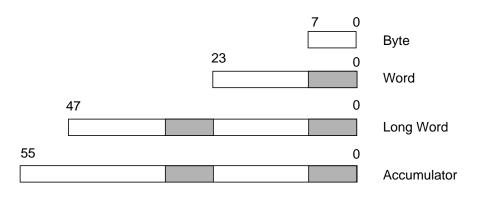

| Figure 3-2.  | Bit Weighting and Alignment of Operands         |

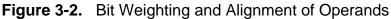

| Figure 3-3.  | Integer/Fractional Multiplication               |

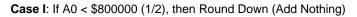

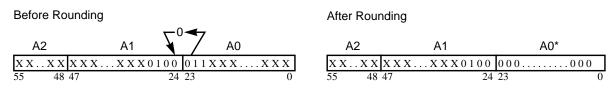

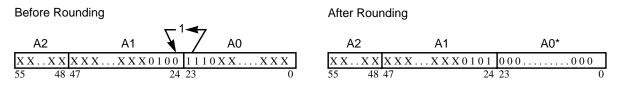

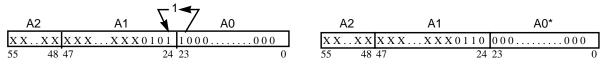

| Figure 3-4.  | Convergent Rounding (No Scaling) 3-9            |

| Figure 3-5.  | Twos Complement Rounding (No Scaling)           |

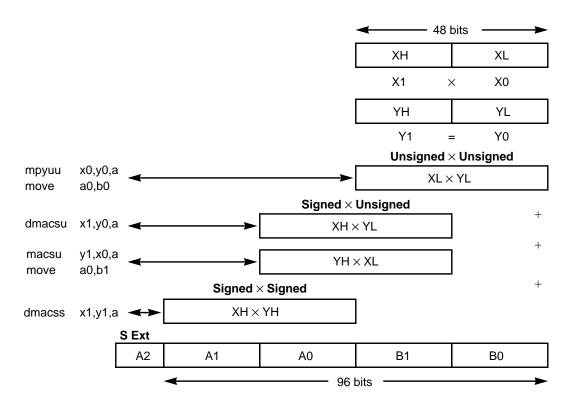

| Figure 3-6.  | DMAC Implementation                             |

| Figure 3-7.  | Double-Precision Multiplication Using DMAC 3-13 |

| Figure 3-8.  | Double-Precision Algorithm                      |

| Figure 3-9.  | Data ALU Core Programming Model.    3-15        |

| Figure 3-10. | Sixteen-Bit Arithmetic Mode Data Organization   |

| Figure 3-11. | Pipeline Conflicts—Arithmetic Stall             |

| Figure 3-12. | Pipeline Conflicts—Status Stall                 |

| Figure 3-13. | Pipeline Conflicts—Transfer Stall               |

| Figure 4-1   | AGU Block Diagram                               |

| Figure 4-2   | AGU Programming Model                           |

| Figure 5-1.  | PCU Architecture                                |

| Figure 5-2.  | Seven-Stage Pipeline                            |

| Figure 5-3.  | PCU Programming Model                           |

| Figure 5-4.  | Operating Mode Register (OMR)                   |

| Figure 5-5.  | Status Register (SR)                            |

| Figure 5-6.  | Stack Pointer (SP) Register Format              |

| Figure 6-1.  | PLL Clock Generator Block Diagram               |

| Figure 6-2.  | PLL Block Diagram                               |

| Figure 6-3.  | CLKGEN Block Diagram                            |

| Figure 6-4.  | PLL Control Register (PCTL)                     |

| Figure 6-5.  | PLL Filter Circuit                              |

| Figure 7-1.  | Test Access Port with OnCE Module Block Diagram |

| Figure 7-2.                                                                                                                                                                                                                                             | TAP Controller State Machine    7-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

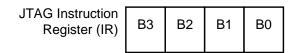

| Figure 7-3.                                                                                                                                                                                                                                             | JTAG Instruction Register Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Figure 7-3.                                                                                                                                                                                                                                             | Identification Register Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

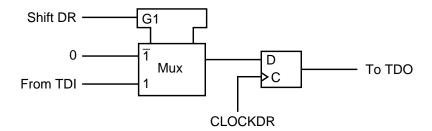

| Figure 7-4.                                                                                                                                                                                                                                             | Bypass Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

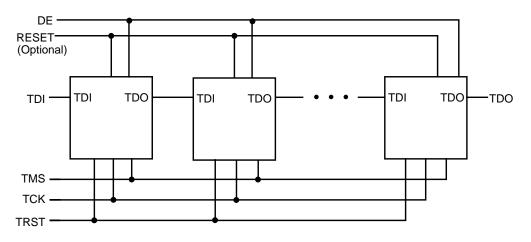

| Figure 7-6.                                                                                                                                                                                                                                             | OnCE Multiprocessor Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

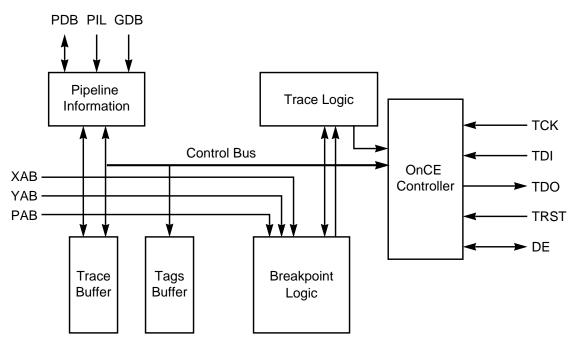

| Figure 7-5.                                                                                                                                                                                                                                             | OnCE Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Figure 7-7.                                                                                                                                                                                                                                             | OnCE Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Figure 7-8.                                                                                                                                                                                                                                             | OnCE Command Register (OCR) Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| Figure 7-9.                                                                                                                                                                                                                                             | OnCE Status and Control Register (OSCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Figure 7-10.                                                                                                                                                                                                                                            | OnCE Memory Breakpoint Logic 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Figure 7-11.                                                                                                                                                                                                                                            | OnCE Breakpoint Control Register (OBCR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Figure 7-12.                                                                                                                                                                                                                                            | Circular Tags Buffer (TAGB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

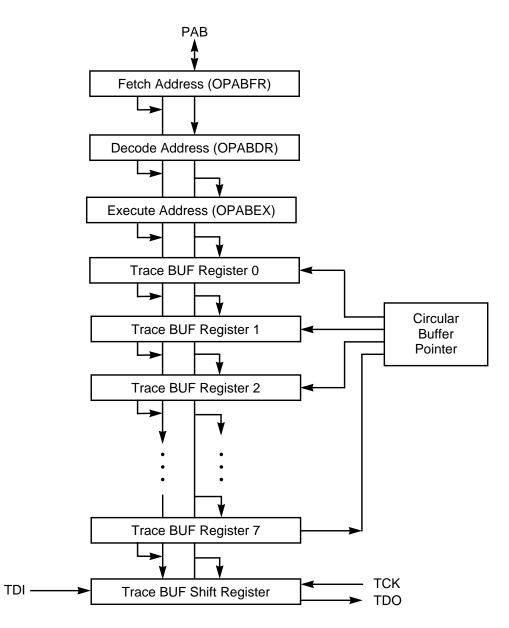

| Figure 7-13.                                                                                                                                                                                                                                            | OnCE Trace Logic Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Figure 7-14.                                                                                                                                                                                                                                            | OnCE Pipeline Information and GDB Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Figure 7-15.                                                                                                                                                                                                                                            | OnCE Trace Buffer Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Figure 8-1.                                                                                                                                                                                                                                             | Instruction Cache Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Figure 9-1.                                                                                                                                                                                                                                             | SRAM Access with One Wait State Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Figure 9-2.                                                                                                                                                                                                                                             | Example SRAM Connection Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

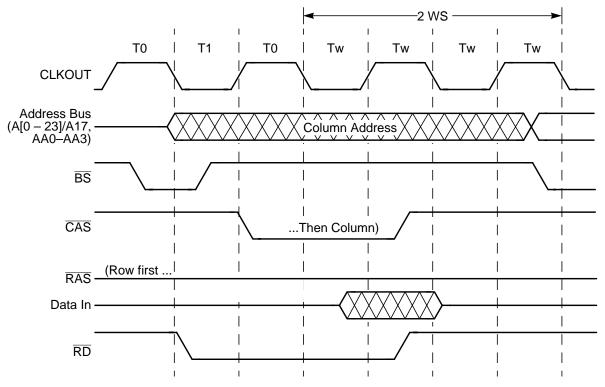

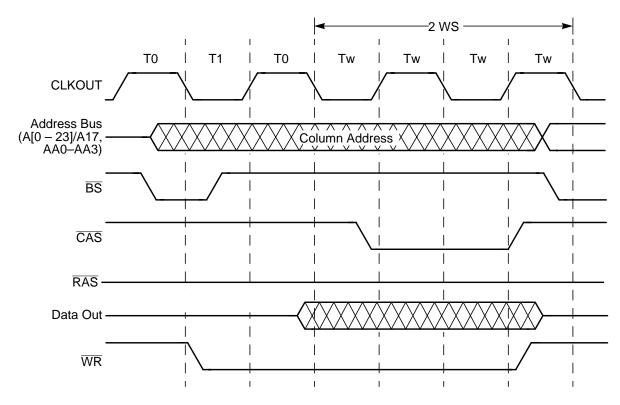

| Figure 9-3.                                                                                                                                                                                                                                             | DRAM Read Access (In-Page) with Two Wait States                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Figure 9-4.                                                                                                                                                                                                                                             | DRAM Write Access (In-Page) with Two Wait States Example                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Figure 9-4.<br>Figure 9-5.                                                                                                                                                                                                                              | DRAM Write Access (In-Page) with Two Wait States Example                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 0                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

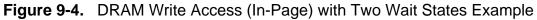

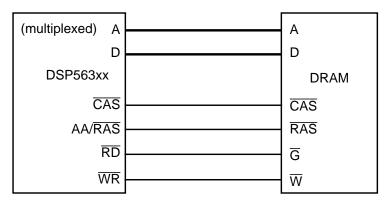

| Figure 9-5.                                                                                                                                                                                                                                             | Typical DRAM Connection Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Figure 9-5.<br>Figure 9-6.                                                                                                                                                                                                                              | Typical DRAM Connection Diagram    9-10      Example Bus Arbitration Scheme    9-13                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.                                                                                                                                                                                                               | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.                                                                                                                                                                                                | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.                                                                                                                                                                 | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21                                                                                                                                                                                                                                                                                                                                         |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.<br>Figure 10-2.                                                                                                                                                 | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21DMA Controller Programming Model10-10                                                                                                                                                                                                                                                                                                    |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.<br>Figure 10-2.<br>Figure 10-3.                                                                                                                                 | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21DMA Controller Programming Model10-10DMA Counter Mode A Layout10-11                                                                                                                                                                                                                                                                      |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.<br>Figure 10-2.<br>Figure 10-3.<br>Figure 10-4.                                                                                                                 | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21DMA Controller Programming Model10-10DMA Counter Mode A Layout10-11DMA Counter Mode B Layout10-12                                                                                                                                                                                                                                        |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.<br>Figure 10-2.<br>Figure 10-3.<br>Figure 10-4.                                                                                                                 | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21DMA Controller Programming Model10-10DMA Counter Mode A Layout10-11DMA Counter Mode B Layout10-12DMA Counter Modes C, D, and E Layouts10-14                                                                                                                                                                                              |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.<br>Figure 10-2.<br>Figure 10-3.<br>Figure 10-4.<br>Figure 10-5.                                                                                                 | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21DMA Controller Programming Model10-10DMA Counter Mode A Layout10-11DMA Counter Mode B Layout10-12DMA Counter Modes C, D, and E Layouts10-14DMA Control Register (DCR)10-16                                                                                                                                                               |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.<br>Figure 10-2.<br>Figure 10-3.<br>Figure 10-4.<br>Figure 10-5.<br>Figure 10-6.                                                                                 | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21DMA Controller Programming Model10-10DMA Counter Mode A Layout10-11DMA Counter Mode B Layout10-12DMA Counter Modes C, D, and E Layouts10-14DMA Control Register (DCR)10-16DMA Status Register (DSTR)10-24                                                                                                                                |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.<br>Figure 10-2.<br>Figure 10-3.<br>Figure 10-4.<br>Figure 10-5.<br>Figure 10-6.<br>Figure 11-1.                                                                 | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21DMA Controller Programming Model10-10DMA Counter Mode A Layout10-11DMA Counter Mode B Layout10-12DMA Counter Modes C, D, and E Layouts10-14DMA Control Register (DCR)10-16DMA Status Register (DSTR)10-24DSP56300 Core Memory Map11-2                                                                                                    |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.<br>Figure 10-2.<br>Figure 10-3.<br>Figure 10-4.<br>Figure 10-5.<br>Figure 10-6.<br>Figure 11-1.<br>Figure 11-2.                                                 | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21DMA Controller Programming Model10-10DMA Counter Mode A Layout10-11DMA Counter Mode B Layout10-12DMA Counter Modes C, D, and E Layouts10-14DMA Control Register (DCR)10-16DMA Status Register (DCR)10-24DSP56300 Core Memory Map11-2DSP56300 Core Memory Map (SC = 1)11-8General Formats of an Instruction Word.12-1                     |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.<br>Figure 10-2.<br>Figure 10-3.<br>Figure 10-4.<br>Figure 10-5.<br>Figure 10-6.<br>Figure 11-1.<br>Figure 11-2.<br>Figure 12-1.                                 | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21DMA Controller Programming Model10-10DMA Counter Mode A Layout10-11DMA Counter Mode B Layout10-12DMA Counter Modes C, D, and E Layouts10-14DMA Control Register (DCR)10-16DMA Status Register (DSTR)10-24DSP56300 Core Memory Map11-2DSP56300 Core Memory Map (SC = 1)11-8General Formats of an Instruction Word.12-1Operand Lengths12-3 |  |  |

| Figure 9-5.<br>Figure 9-6.<br>Figure 9-7.<br>Figure 9-8.<br>Figure 9-9.<br>Figure 10-1.<br>Figure 10-2.<br>Figure 10-3.<br>Figure 10-4.<br>Figure 10-5.<br>Figure 10-6.<br>Figure 11-1.<br>Figure 11-2.<br>Figure 12-1.<br>Figure 12-2.<br>Figure 12-3. | Typical DRAM Connection Diagram9-10Example Bus Arbitration Scheme9-13Address Attribute Registers (AAR0–AAR3)9-16Bus Control Register (BCR)9-19DRAM Control Register (DCR)9-21DMA Controller Programming Model10-10DMA Counter Mode A Layout10-11DMA Counter Mode B Layout10-12DMA Counter Modes C, D, and E Layouts10-14DMA Control Register (DCR)10-16DMA Status Register (DSTR)10-24DSP56300 Core Memory Map11-2DSP56300 Core Memory Map (SC = 1)11-8General Formats of an Instruction Word.12-1Operand Lengths12-3 |  |  |

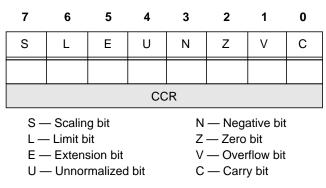

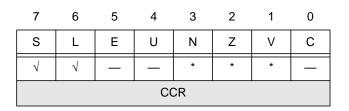

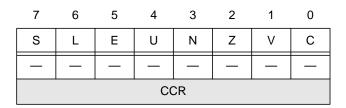

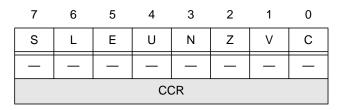

| Figure 12-6. | Condition Code Register (CCR) 12-18     |

|--------------|-----------------------------------------|

| Figure A-1.  | Types of Address Generation Interlock   |

| Figure B-1.  | True (Exact) LMS Adaptive Filter B-21   |

| Figure B-2.  | FIR Lattice FilterB-26                  |

| Figure B-3.  | All Pole IIR Lattice Filter             |

| Figure B-4.  | General Lattice Filter                  |

| Figure B-5.  | Normalized Lattice Filter               |

| Figure B-6.  | FIR Filtering                           |

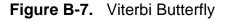

| Figure B-7.  | Viterbi ButterflyB-38                   |

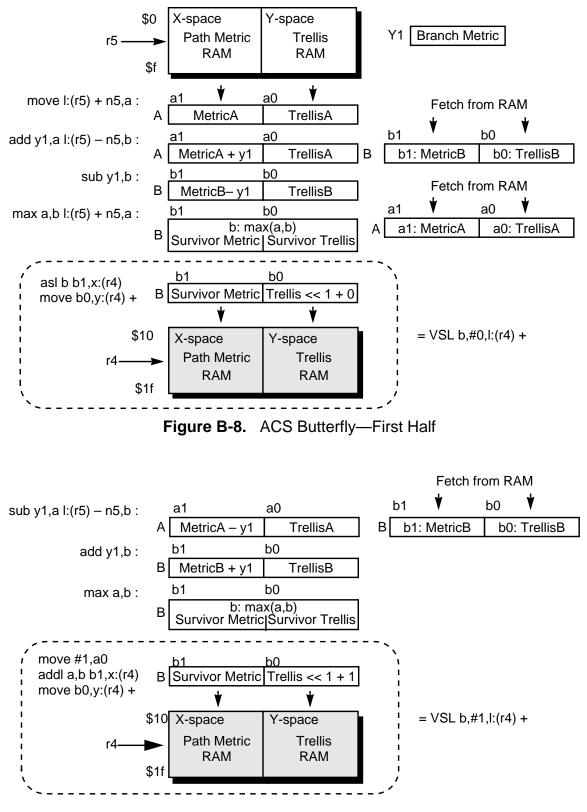

| Figure B-8.  | ACS Butterfly—First HalfB-39            |

| Figure B-9.  | ACS Butterfly—Second Half               |

| Figure B-10. | Parsing Process                         |

| Figure C-1.  | CDR/HIP DMA and Core Access Comparisons |

## Tables

| Table 1-1         | DSP Family Manual Chapters 1-                                    | 13  |

|-------------------|------------------------------------------------------------------|-----|

| Table 2-1         | Instruction Pipeline                                             | -5  |

| Table 2-2         | Interrupt Sources                                                | -7  |

| Table 2-3         | Status Register Interrupt Mask Bits 2-                           | 10  |

| Table 2-4         | Interrupt Priority Level Bits 2-                                 | 11  |

| Table 2-5         | External Interrupt Trigger Mode Bit 2-                           | 11  |

| Table 2-6         | Exception Priorities Within an IPL 2-                            | 11  |

| Table 2-7         | Fast Interrupt Pipeline                                          | 14  |

| Table 2-8         | Long Interrupt Pipeline                                          | 15  |

| Table 3-1         | Actions of the Arithmetic Saturation Mode ( $SM = 1$ )           | 11  |

| Table 3-2         | Acceptable Signed and Unsigned Twos-Complement Multiplication 3- | 12  |

| Table 3-3         | Moves into Registers or Accumulators                             | 17  |

| Table 3-4         | Moves from Registers or Accumulators 3-                          | 18  |

| Table 4-5         | Addressing Modes Summary 4                                       | 6   |

| Table 4-6         | Address Modifier Type Encoding Summary 4-                        | 11  |

| Table 5-1         | Seven-Stage Pipeline                                             | -4  |

| Table 5-2         | Operating Mode Register Bit Definitions                          | -7  |

| Table 5-3         | Status Register Bit Definitions                                  |     |

| Table 5-4         | Stack Pointer (SP) Register Bit Definitions                      | 21  |

| Table 6-1.        | PLL Control Register (PCTL) Bit Definitions                      | -7  |

| Table 7-1.        | Debugging Control Signals                                        | -1  |

| <b>Table 7-2.</b> | JTAG Instructions                                                | -6  |

| <b>Table 7-3.</b> | OnCE Command Register (OCR) Bit Definitions                      | 13  |

| Table 7-4.        | OnCE Status and Control Register (OSCR) Bit Definitions          | 16  |

| Table 7-5.        | OnCE Breakpoint Control Register (OBCR) Bit Definitions          | 19  |

| Table 7-6.        | TMS Sequencing for DEBUG_REQUEST and Poll the Status             |     |

| Table 7-7.        | TMS Sequencing for ENABLE_ONCE                                   |     |

| <b>Table 7-8.</b> | TMS Sequencing for Reading Pipeline Register                     | 35  |

| Table 8-1.        | Determining the Number of Required Fetches in Burst Mode         | -5  |

| Table 9-1         | External Address Bus Signals                                     |     |

| Table 9-2         | External Data Bus Signals                                        | -2  |

| Table 9-3         | External Bus Control Signals                                     | )-2 |

| Table 9-4         | AAR Bit Definitions                                              |     |

| Table 9-5         | Bus Control Register (BCR) Bit Definitions                       | 19  |

| Table 9-6         | DRAM Control Register (DCR) Bit Definitions9-                    | 22  |

| Table 10-1        | DMA Controller Data Transfers 10                                 | -2  |

| <b>Table 10-2</b>   | Interaction Between the DSR and DCO in Mode A                | . 10-12 |  |  |

|---------------------|--------------------------------------------------------------|---------|--|--|

| Table 10-3          | Interaction Between the DSR and DCO in Mode B 10-13          |         |  |  |

| Table 10-4          | Interaction Between the DSR and DCO in Mode C, D, or E 10-15 |         |  |  |

| Table 10-5          | DMA Control Register (DCR) Bit Definitions                   |         |  |  |

| Table 10-6          | Address Generation Mode (D3D = 0) 10-                        |         |  |  |

| <b>Table 10-7</b>   | Address Generation Mode $(D3D = 1)$                          |         |  |  |

| Table 10-8          | Address Mode Select (D3D = 1)                                | . 10-23 |  |  |

| <b>Table 10-9</b>   | Counter Mode (D3D = 1)                                       | . 10-23 |  |  |

| <b>Table 10-10</b>  | DMA Status Register (DSTR) Bit Definitions                   | . 10-25 |  |  |

| <b>Table 11-1.</b>  | DSP Core Operating Modes                                     |         |  |  |

| <b>Table 11-2.</b>  | DSP Core Reset Vectors, Possible Values                      | 11-1    |  |  |

| <b>Table 11-3.</b>  | Internal X I/O Space Map                                     | 11-3    |  |  |

| <b>Table 12-1.</b>  | Parallel Instruction Format                                  | 12-2    |  |  |

| <b>Table 12-2.</b>  | Non-Parallel Instruction Format                              | 12-3    |  |  |

| <b>Table 12-3.</b>  | Register Operand Lengths                                     | 12-4    |  |  |

| <b>Table 12-4.</b>  | Arithmetic Instructions                                      | 12-7    |  |  |

| <b>Table 12-5.</b>  | Logical Instructions                                         | 12-9    |  |  |

| <b>Table 12-6.</b>  | Bit Manipulation Instructions                                | . 12-11 |  |  |

| <b>Table 12-7.</b>  | Loop Instructions                                            | . 12-11 |  |  |

| <b>Table 12-8.</b>  | Move Instructions                                            | . 12-12 |  |  |

| <b>Table 12-9.</b>  | Program Control Instructions                                 | . 12-12 |  |  |

| <b>Table 12-10.</b> | Instruction Description Notation                             | . 12-14 |  |  |

| <b>Table 12-11.</b> | Instruction Effect on Condition Code                         | . 12-19 |  |  |

| <b>Table 12-12.</b> | Condition Code Register (CCR) Bit Definitions                | . 12-19 |  |  |

| Table 12-13.        | Partial Encodings for Use in Instruction Encoding            | . 12-22 |  |  |

| <b>Table 12-14.</b> | Triple-Bit Register Encoding                                 | . 12-24 |  |  |

| <b>Table 12-15.</b> | Long Move Register Encoding                                  | . 12-24 |  |  |

| <b>Table 12-16.</b> | Partial Encodings for Use in Instructions Encoding, 2        | . 12-24 |  |  |

| <b>Table 12-17.</b> | Condition Code Computation Equation                          | . 12-28 |  |  |

| <b>Table 12-18.</b> | Condition Codes Encoding                                     | . 12-28 |  |  |

| Table 12-19.        | Operation Code K0–2 Decode                                   | . 12-29 |  |  |

| <b>Table 12-20.</b> | Non-Multiply Instruction Encoding                            | . 12-30 |  |  |

| Table 12-21.        | Special Case1                                                | . 12-30 |  |  |

| Table 13-1.         | DSP56300 Instruction Summary                                 |         |  |  |

| Table 12-14.        | Move Instructions                                            | 13-110  |  |  |

| Table A-1.          | Instruction Timing, Word Count, and Encoding                 | A-2     |  |  |

| Table A-2.          | Instructions That Access the System Stack                    | A-14    |  |  |

| Table A-3.          | Stack Extension Delays                                       |         |  |  |

| Table B-1.          | List of Benchmark Programs                                   | B-1     |  |  |

| Table B-2.          | Example of Assembly Language Source                          | B-2     |  |  |

| Table B-3.  | Real MultiplyB-3                                                      |

|-------------|-----------------------------------------------------------------------|

| Table B-4.  | N Real Multiplies Memory MapB-4                                       |

| Table B-5.  | N Real Updates Memory MapB-6                                          |

| Table B-6.  | Real Correlation or Convolution (FIR Filter) Memory MapB-7            |

| Table B-7.  | Real * Complex Correlation or Convolution (FIR Filter) Memory Map B-8 |

| Table B-8.  | Complex Multiply Memory Map B-10                                      |

| Table B-9.  | N Complex Multiplies Memory MapB-11                                   |

| Table B-10. | Complex Update Memory Map B-12                                        |

| Table B-11. | N Complex Updates Memory MapB-13                                      |

| Table B-12. | N Complex Updates Memory MapB-14                                      |

| Table B-13. | Complex Correlation or Convolution (FIR Filter) Memory MapB-15        |

| Table B-1.  | Second Order Real Biquad IIR Filter Memory MapB-18                    |

| Table B-2.  | N Cascaded Real Biquad IIR Filter Memory MapB-19                      |

| Table B-3.  | N Cascaded Real Biquad IIR FilterB-19                                 |

| Table B-4.  | N Radix-2 FFT Butterflies (DIT, In-Place Algorithm) Memory Map B-20   |

| Table B-5.  | System EquationsB-21                                                  |

| Table B-6.  | LMS AlgorithmsB-21                                                    |

| Table B-7.  | True (Exact) LMS Adaptive Filter Memory MapB-22                       |