# PCI 9656BA Data Book

Version 1.3

January2009Websitewww.plxtech.comTechnical Supportwww.plxtech.com/supportPhone800 759-3735408 774-9060FAX408 774-2169

#### **COPYRIGHT INFORMATION**

Copyright © 2003 – 2009 PLX Technology, Inc. All Rights Reserved. The information in this document is proprietary and confidential to PLX Technology. No part of this document may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without written permission from PLX Technology.

PLX Technology provides this documentation without warranty, term or condition of any kind, either express or implied, including, but not limited to, express and implied warranties of merchantability, fitness for a particular purpose, and non-infringement. While the information contained herein is believed to be accurate, such information is preliminary, and no representations or warranties of accuracy or completeness are made. In no event will PLX Technology be liable for damages arising directly or indirectly from any use of or reliance upon the information contained in this document. PLX Technology may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

PLX Technology retains the right to make changes to this product at any time, without notice. Products may have minor variations to this publication, known as errata. PLX Technology assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of PLX Technology products.

PLX Technology, the PLX logo, and Data Pipe Architecture are registered trademarks of PLX Technology, Inc.

HyperTransport is a trademark of the HyperTransport Technology Consortium.

Tri-State is a registered trademark of National Semiconductor Corporation.

Other brands and names are the property of their respective owners.

Document Number: 9656BA-SIL-DB-P1-1.3

### Contents

| Figures   |                                                                         | xi   |

|-----------|-------------------------------------------------------------------------|------|

| Tables .  |                                                                         | xiii |

| Registe   | rs                                                                      | xvii |

| Timing I  | Diagrams                                                                | xxi  |

| Preface   |                                                                         | xxv  |

|           | Supplemental Documentation                                              | xxv  |

|           | Terms and Definitions                                                   | xxvi |

|           | Revision History                                                        | xxvi |

| Feature   | Summary                                                                 | xxix |

| 1. Introd | duction                                                                 | 1-1  |

|           | 1.1. Company and Draduat Background                                     | 1 1  |

|           | 1.1. Company and Product Background                                     |      |

|           | 1.2. Data Pipe Architecture Technology                                  |      |

|           | 1.2.1. High-Speed Data Transfers         1.2.1.1. Direct Transfers      |      |

|           | 1.2.1.1.1. Direct Master                                                |      |

|           | 1.2.1.1.2. Direct Slave                                                 |      |

|           | 1.2.1.1.2. DNet Glave                                                   |      |

|           | 1.2.1.2.1. DMA Block Mode                                               |      |

|           | 1.2.1.2.2. DMA Scatter/Gather Mode                                      |      |

|           | 1.2.1.2.3. Hardware DMA Controls – EOT and Demand Mode                  |      |

|           | 1.2.2. Intelligent Messaging Unit                                       |      |

|           | 1.3. PCI 9656 I/O Accelerator                                           |      |

|           | 1.3.1. Applications                                                     |      |

|           | 1.3.1.1. High-Performance Motorola MPC850 and MPC860 PowerQUICC Designs | 1-4  |

|           | 1.3.1.2. High-Performance CompactPCI Adapter Cards                      | 1-5  |

|           | 1.3.1.3. High-Performance PCI Adapter Cards                             |      |

|           | 1.3.1.4. High-Performance Embedded Host Designs                         |      |

|           | 1.4. Major Features                                                     | 1-8  |

|           | 1.4.1. Interfaces                                                       |      |

|           | 1.4.2. Data Transfer                                                    |      |

|           | 1.4.3. Messaging Unit                                                   |      |

|           | 1.4.4. Hosting Features                                                 |      |

|           | 1.4.5. Electrical/Mechanical                                            |      |

|           | 1.4.6. Miscellaneous         1.5. Compatibility with Other PLX Chips    |      |

|           | 1.5.1. Pin Compatibility                                                |      |

|           | 1.5.2. Register Compatibility                                           |      |

|           | 1.5.3. PCI 9656 Comparison with Other PLX Chips                         |      |

|           |                                                                         | 1-11 |

| 2. M Mode Bus Operation                                | 2-1 |

|--------------------------------------------------------|-----|

| 2.1. PCI Bus Cycles                                    |     |

| 2.1.1. Direct Slave Command Codes                      |     |

| 2.1.2. PCI Master Command Codes                        |     |

| 2.1.2.1. DMA Master Command Codes                      |     |

| 2.1.2.2. Direct Master Local-to-PCI Command Codes.     |     |

| 2.1.3. PCI Arbitration                                 |     |

| 2.1.4. PCI Bus Wait States                             |     |

| 2.2. Local Bus Cycles                                  |     |

| 2.2.1. Local Bus Arbitration                           |     |

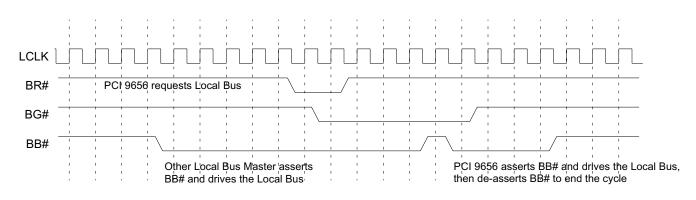

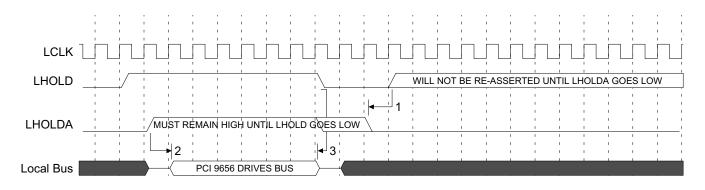

| 2.2.1.1. Local Bus Arbitration Timing Diagram          |     |

| 2.2.2. Direct Master                                   |     |

| 2.2.3. Direct Slave                                    |     |

| 2.2.4. Wait State Control                              |     |

| 2.2.4.1. Local Bus Wait States.                        |     |

| 2.2.5. Data Transfer Modes                             |     |

| 2.2.5.1. Single Cycle Mode                             |     |

| 2.2.5.1.1. Partial Data Accesses                       |     |

| 2.2.5.2. Burst-4 Mode                                  |     |

| 2.2.5.2.1. Partial Data (<4 Bytes) Accesses            |     |

| 2.2.5.3. Continuous Burst Mode                         |     |

| 2.2.6. Local Bus Read Accesses                         |     |

| 2.2.7. Local Bus Write Accesses                        |     |

| 2.2.8. Direct Slave Accesses to 8- or 16-Bit Local Bus |     |

| 2.2.9. Local Bus Data Parity                           |     |

| 2.3. Big Endian/Little Endian                          |     |

| 2.3.1. PCI Bus Data Bits Mapping onto Local Bus        |     |

| 2.4. Serial EEPROM                                     |     |

| 2.4.1. PCI 9656 Initialization from Serial EEPROM      |     |

| 2.4.2. Local Initialization and PCI Bus Behavior       |     |

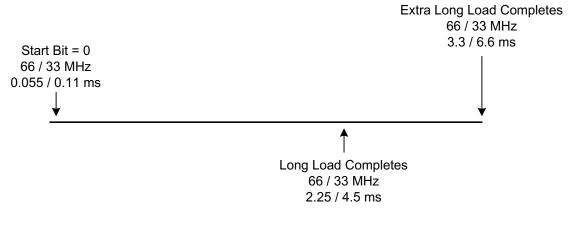

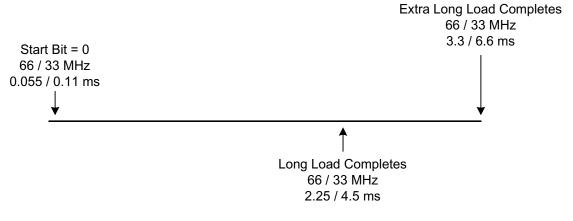

| 2.4.2.1. Long Serial EEPROM Load                       |     |

| 2.4.2.2. Extra Long Serial EEPROM Load.                |     |

| 2.4.3. Serial EEPROM Access                            |     |

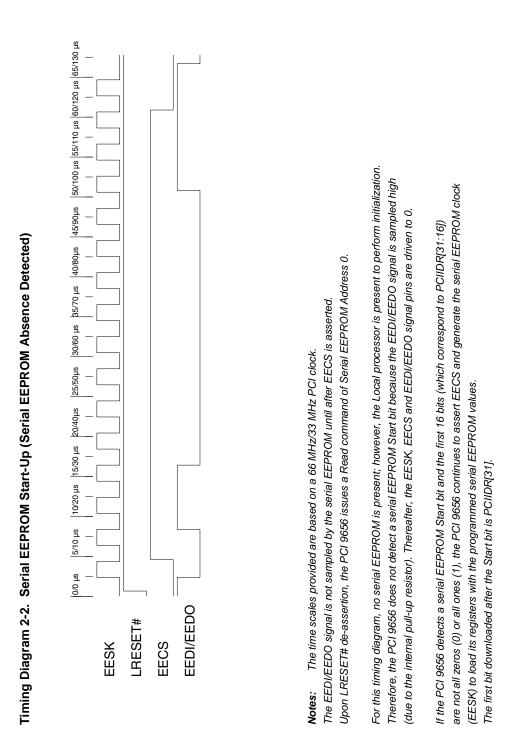

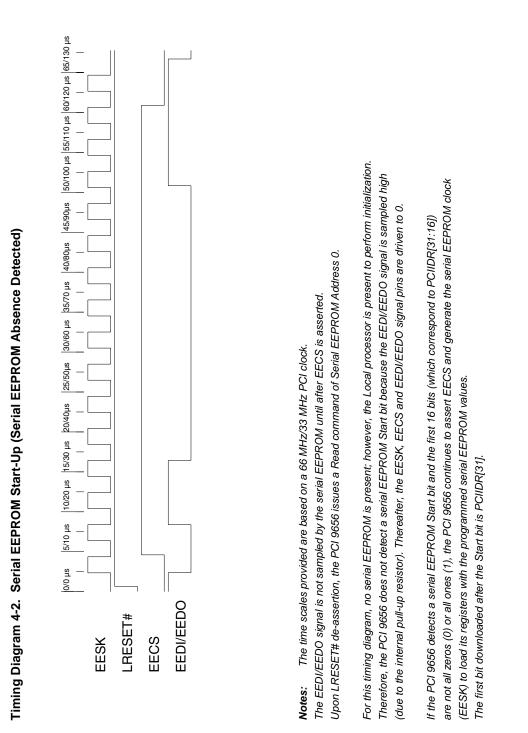

| 2.4.4. Serial EEPROM Initialization Timing Diagram     |     |

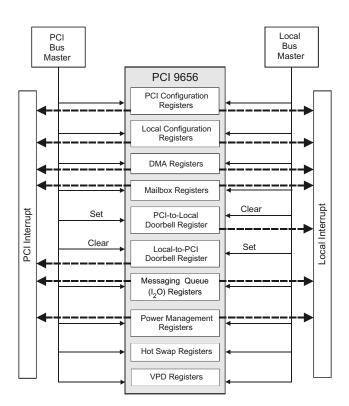

| 2.5. Internal Register Access                          |     |

| 2.5.1. PCI Bus Access to Internal Registers            |     |

| 2.5.1.1. New Capabilities Function Support.            |     |

| 2.5.2. Local Bus Access to Internal Registers          |     |

|                                                        |     |

| 3. M Mode Functional Description                       | 3-1 |

|                                                        | 3-1 |

| 3.1. Reset Operation                                   | 3-1 |

| 3.1.1. Adapter Mode                                    |     |

| 3.1.1.1. PCI Bus RST# Input                            |     |

| 3.1.1.2. JTAG Reset TRST# Input.                       |     |

| 3.1.1.3. Software Reset                                |     |

| 3.1.1.4. Power Management Reset                        |     |

| 3.1.2. Host Mode                                       |     |

| 3.1.2.1. Local Reset                                   |     |

| 3.1.2.2. Software Reset                                |     |

3.1.2.3. Power Management Reset

3-2

3.2. PCI 9656 Initialization

3-2

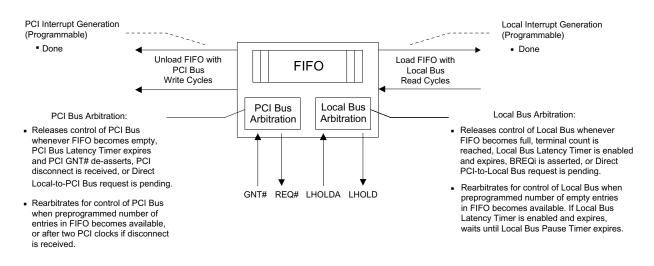

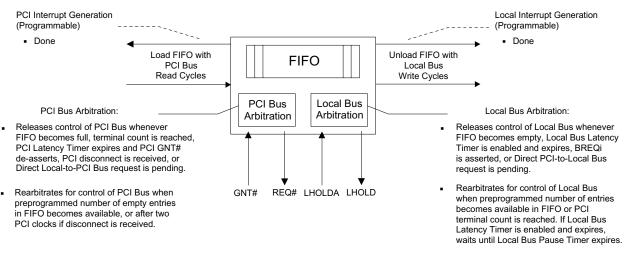

3.3. Response to FIFO Full or Empty

3-3

3.4. Direct Data Transfer Modes

3-4

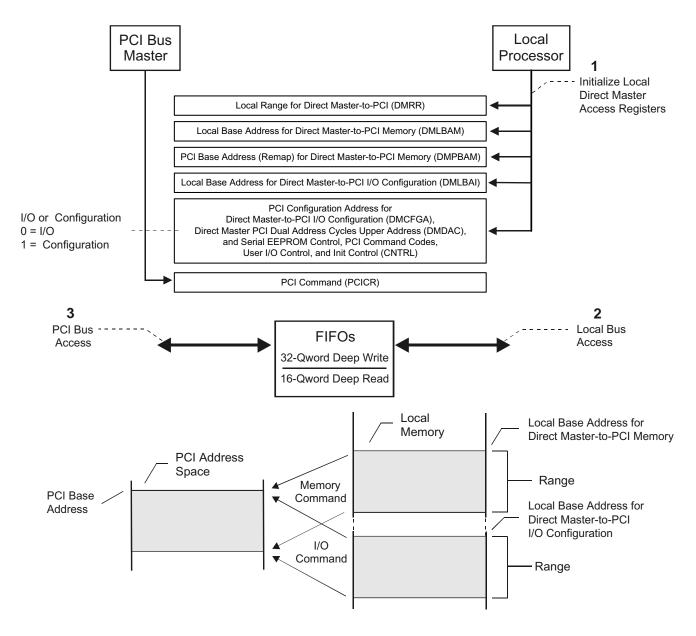

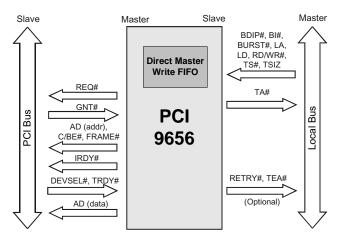

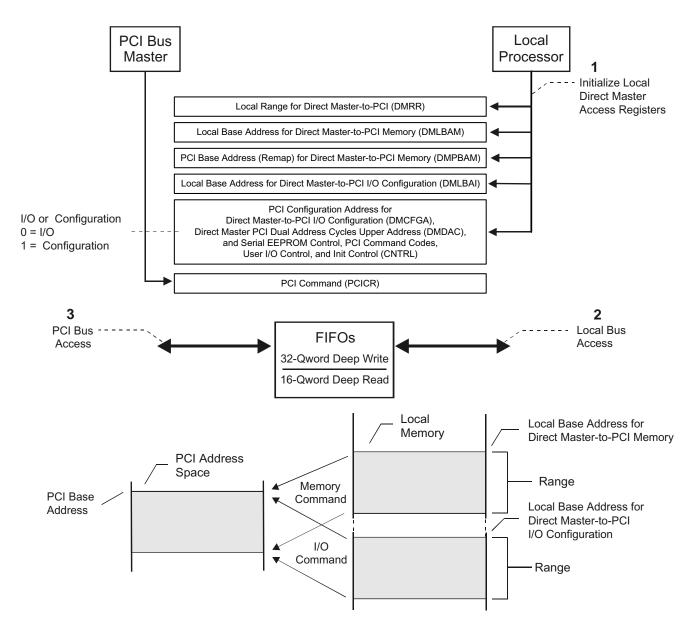

3.4.1. Direct Master Operation (Local Master-to-PCI Slave)

3-4

3.4.1.1. Direct Master Memory and I/O Decode

3-4

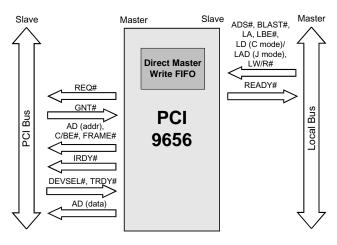

3.4.1.2. Direct Master FIFOs

3-6

| 3.4.1.3. Direct Master Memory Access                                                                |      |

|-----------------------------------------------------------------------------------------------------|------|

| 3.4.1.3.1. Direct Master Writes                                                                     |      |

| 3.4.1.3.2. Direct Master Reads                                                                      |      |

| 3.4.1.4. Direct Master I/O.                                                                         |      |

| 3.4.1.5. Direct Master Delayed Read Mode.                                                           |      |

| 3.4.1.6. Direct Master Delayed Write Mode.                                                          |      |

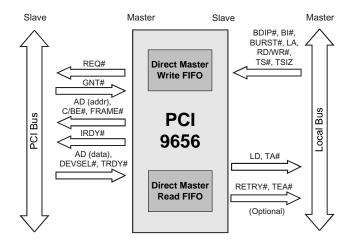

| 3.4.1.7. Direct Master Read Ahead Mode                                                              |      |

| 3.4.1.8. RETRY# Capability.                                                                         |      |

| 3.4.1.9. Direct Master Configuration (PCI Type 0 or Type 1 Configuration Cycles)                    |      |

| 3.4.1.9.1. Direct Master Configuration Cycle Example                                                |      |

| 3.4.1.10. Direct Master PCI Dual Address Cycles                                                     |      |

| 3.4.1.11. PCI Master/Target Abort.         3.4.1.12. Direct Master Memory Write and Invalidate      |      |

|                                                                                                     |      |

| 3.4.1.13. IDMA/SDMA Operation.                                                                      |      |

| 3.4.1.13.1. IDMA Operation                                                                          |      |

| 3.4.1.13.2. SDMA Operation                                                                          |      |

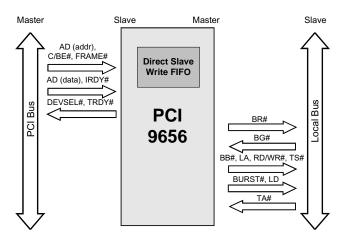

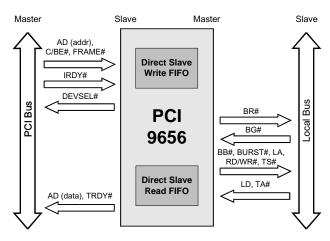

| 3.4.2. Direct Slave Operation (PCI Master-to-Local Bus Access)         3.4.2.1. Direct Slave Writes |      |

| 3.4.2.1. Direct Slave Writes                                                                        |      |

| 3.4.2.3. Direct Slave Lock                                                                          |      |

|                                                                                                     |      |

| 3.4.2.4. <i>PCI r2.2</i> -Compliance Enable                                                         |      |

| 3.4.2.4.2. 2 <sup>15</sup> PCI Clock Timeout                                                        |      |

| 3.4.2.4.3. <i>PCI r</i> 2.2 16- and 8-Clock Rule                                                    | 2 17 |

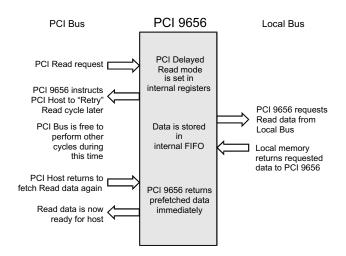

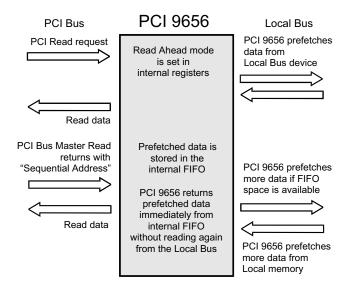

| 3.4.2.5. Direct Slave Read Ahead Mode                                                               |      |

| 3.4.2.5. Direct Slave Read Allead Mode                                                              |      |

| 3.4.2.7. Direct Slave Local Bus TA# Timeout Mode                                                    |      |

| 3.4.2.7. Direct Slave Local Bus TA# Timeout Mode                                                    |      |

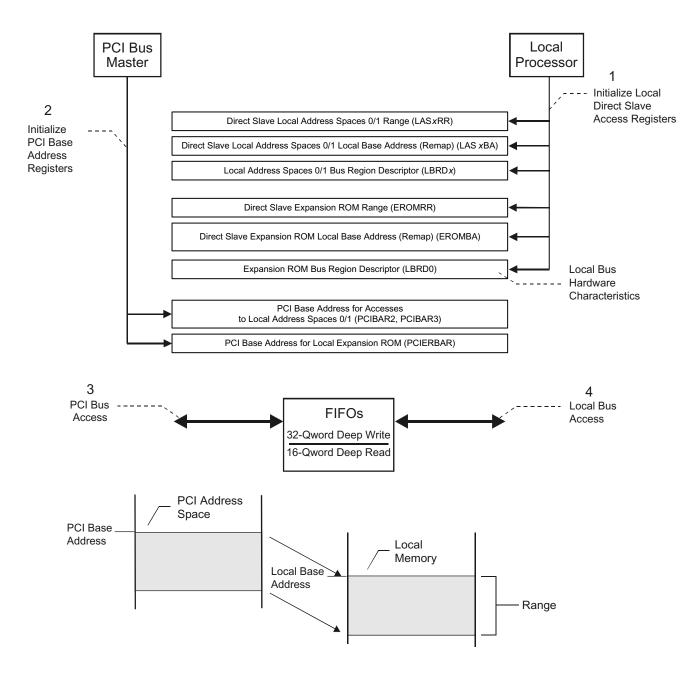

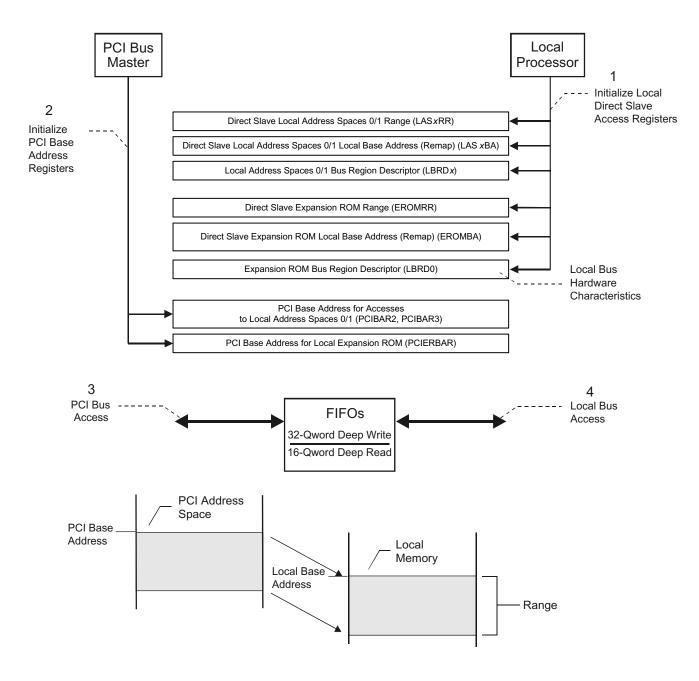

| 3.4.2.9. Direct Slave PCI-to-Local Address Mapping.                                                 |      |

| 3.4.2.9. Direct Slave FCI-to-Local Address Mapping                                                  |      |

| 3.4.2.9.2. Direct Slave PCI Initialization                                                          |      |

| 3.4.2.9.3. Direct Slave PCI Initialization Example                                                  |      |

| 3.4.2.9.4. Direct Slave For Initialization Example                                                  |      |

| 3.4.2.10. Direct Slave Priority                                                                     |      |

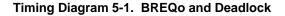

| 3.4.3. Deadlock Conditions                                                                          |      |

| 3.4.3.1. Backoff                                                                                    |      |

| 3.4.3.1.1. Software/Hardware Solution for Systems without Backoff Capability                        |      |

| 3.4.3.1.2. Preempt Solution                                                                         |      |

| 3.4.3.2. Software Solutions to Deadlock                                                             |      |

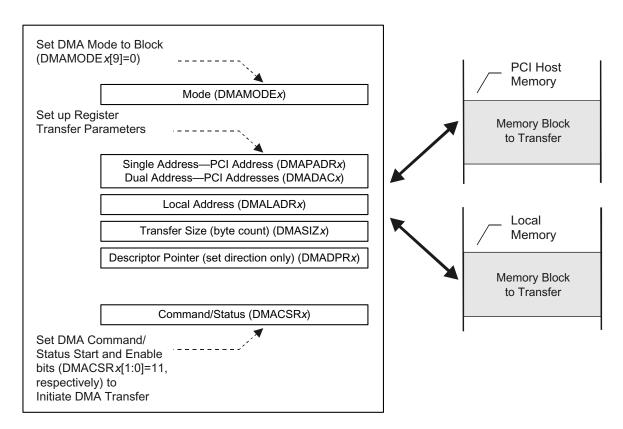

| 3.4.4. DMA Operation                                                                                |      |

| 3.4.4.1. DMA PCI Dual Address Cycles                                                                |      |

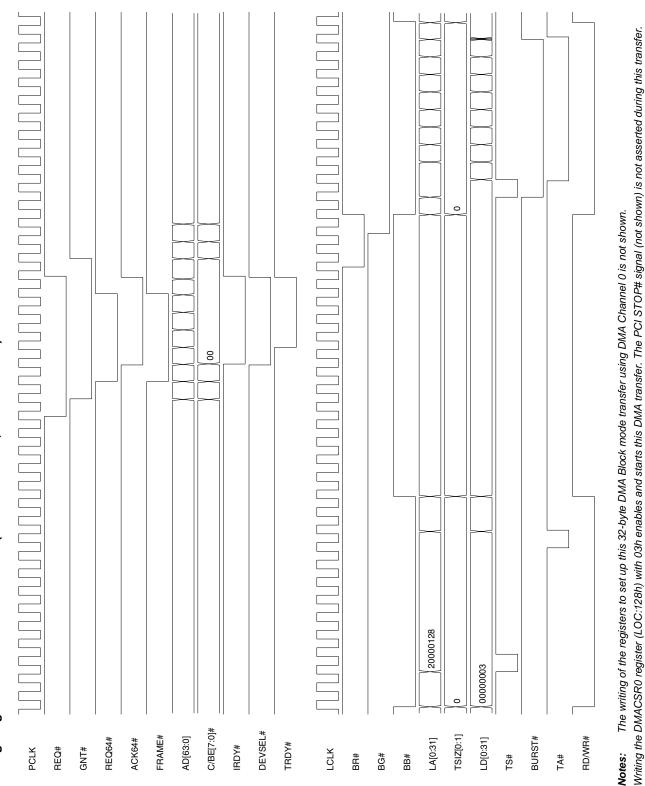

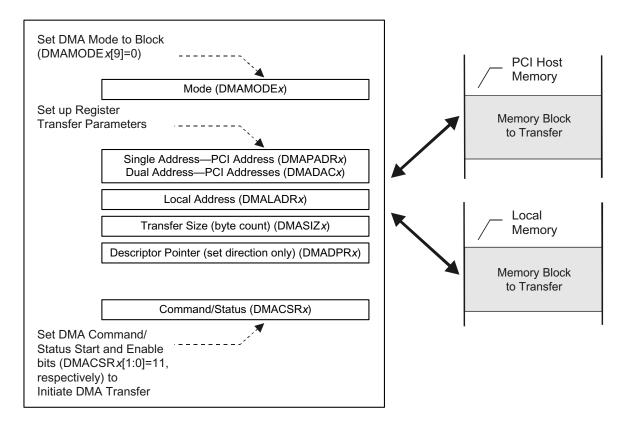

| 3.4.4.2. DMA Block Mode                                                                             |      |

| 3.4.4.2.1. DMA Block Mode PCI Dual Address Cycles                                                   |      |

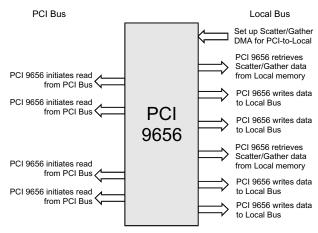

| 3.4.4.3. DMA Scatter/Gather Mode                                                                    |      |

| 3.4.4.3.1. DMA Scatter/Gather PCI Dual Address Cycles                                               |      |

| 3.4.4.3.2. DMA Clear Count Mode                                                                     |      |

| 3.4.4.3.3. DMA Ring Management (Valid Mode)                                                         |      |

| 3.4.4.4. DMA Memory Write and Invalidate                                                            |      |

| 3.4.4.5. DMA Abort                                                                                  |      |

| 3.4.4.6. DMA Channel Priority                                                                       |      |

| 3.4.4.7. DMA Channel <i>x</i> Interrupts                                                            |      |

| 3.4.4.8. DMA Data Transfers                                                                         |      |

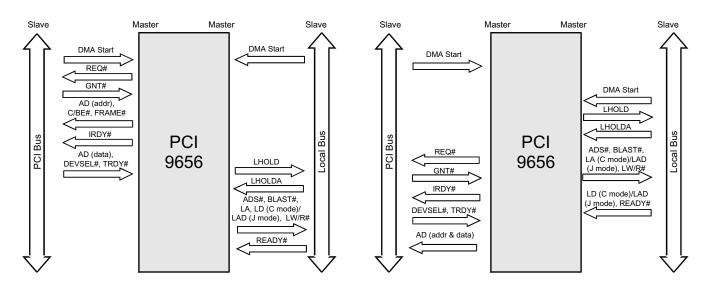

| 3.4.4.8.1. Local-to-PCI Bus DMA Transfer                                                            |      |

| 3.4.4.8.2. PCI-to-Local Bus DMA Transfer                                                            |      |

| 3.4.4.9. DMA Local Bus Error Condition                                                              |      |

| 3.4.4.10. DMA Unaligned Transfers                                                                   |      |

|                                                                                                     |      |

| 3.4.4.11. DMA Demand Mode, Channel <i>x</i>  | 3-34 |

|----------------------------------------------|------|

| 3.4.4.11.1. Fast/Slow Terminate Mode         | 3-35 |

| 3.4.4.11.2. PCI-to-Local DMA Demand Mode     | 3-35 |

| 3.4.4.11.3. Local-to-PCI DMA Demand Mode     | 3-37 |

| 3.4.4.12. End of Transfer (EOT#) Input       | 3-39 |

| 3.4.4.13. DMA Arbitration                    | 3-39 |

| 3.4.4.14. Local Bus DMA Priority             | 3-40 |

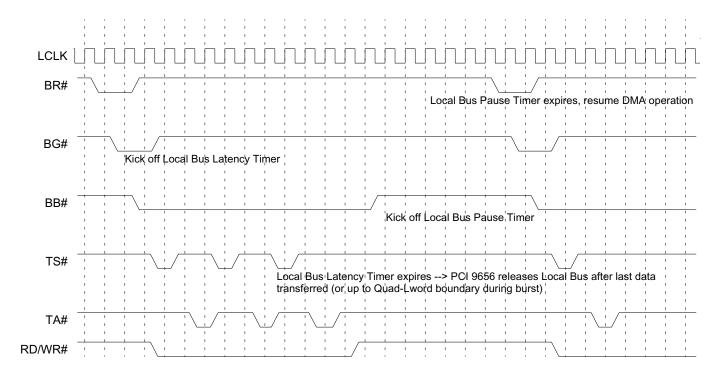

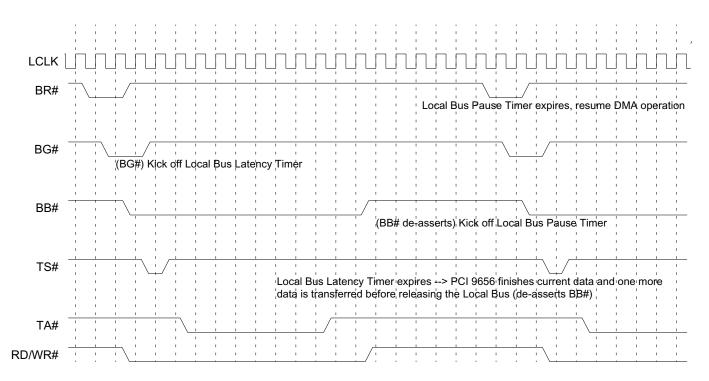

| 3.4.4.15. Local Bus Latency and Pause Timers | 3-40 |

| 3.4.4.16. DMA FIFO Programmable Threshold    | 3-40 |

| 3.4.4.17. DMA PCI Master/Target Abort        | 3-42 |

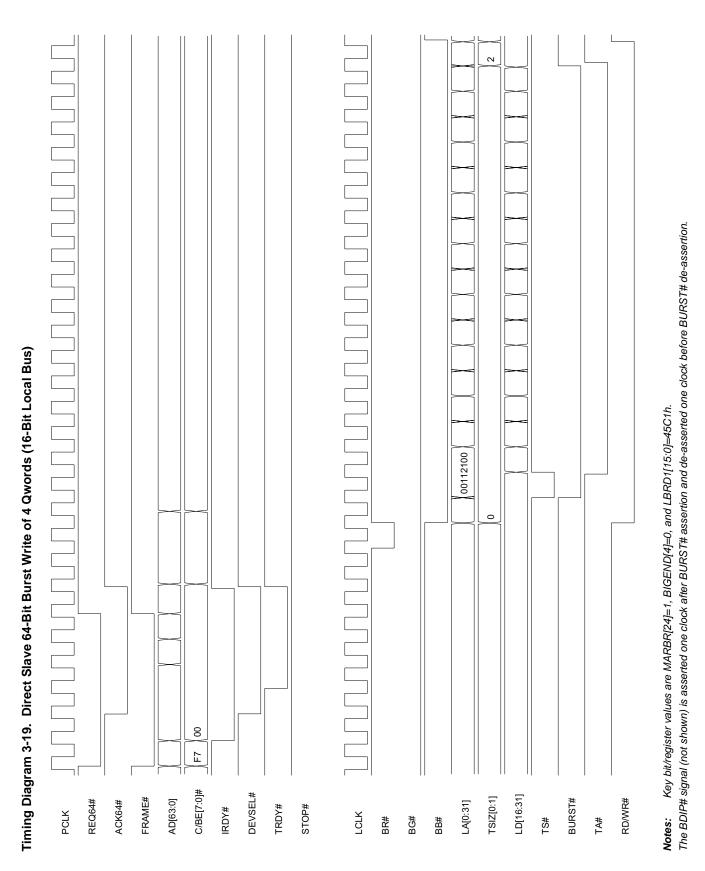

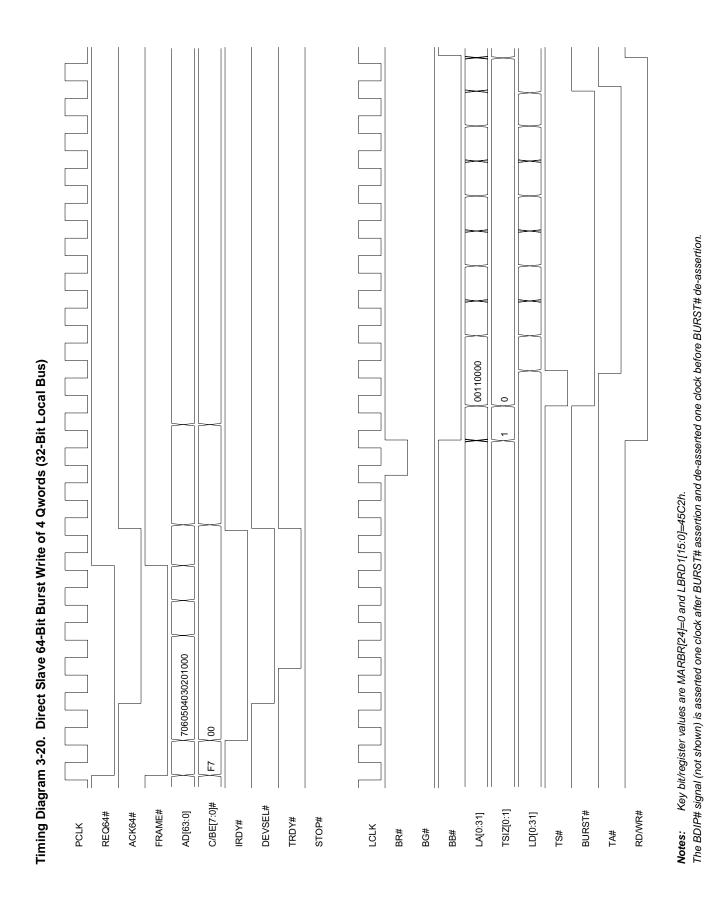

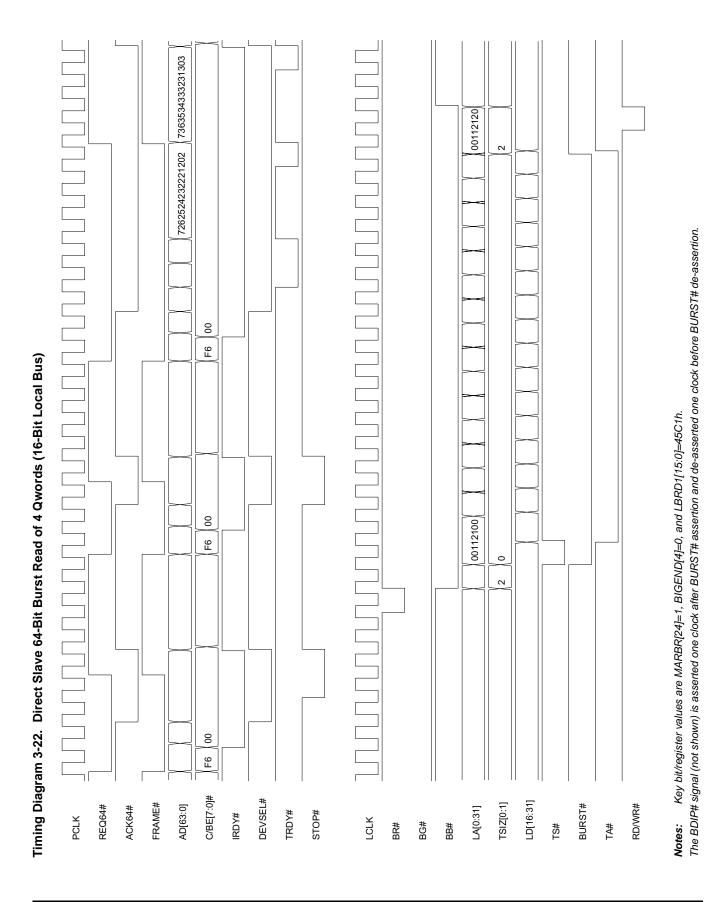

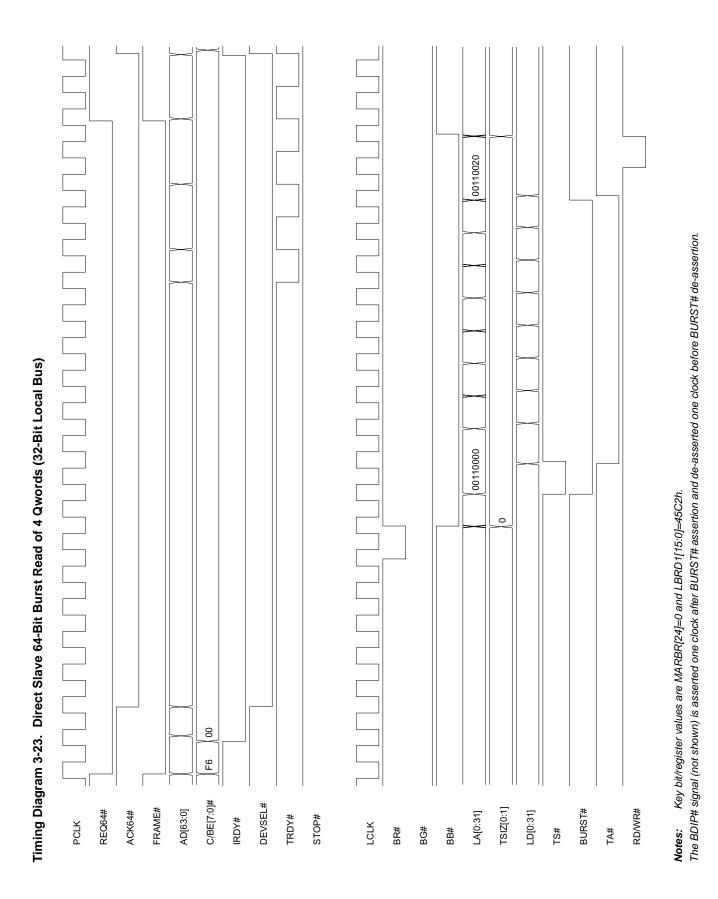

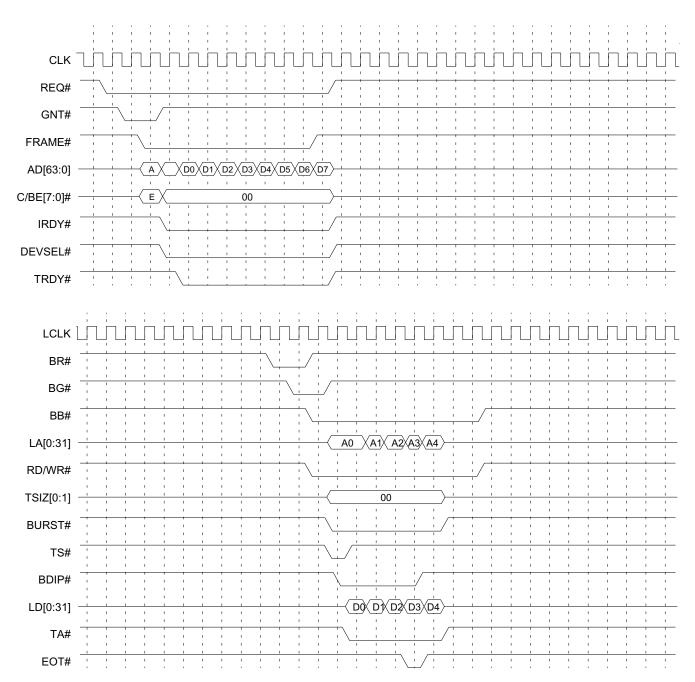

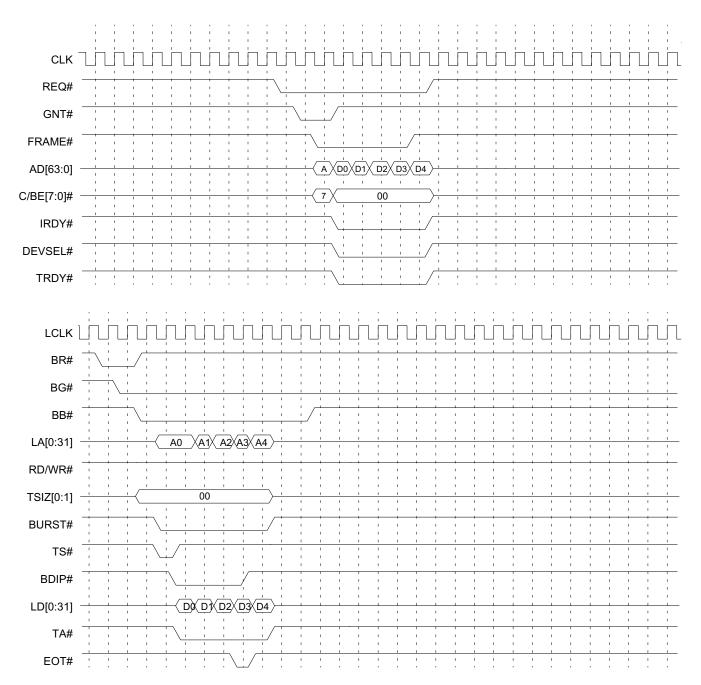

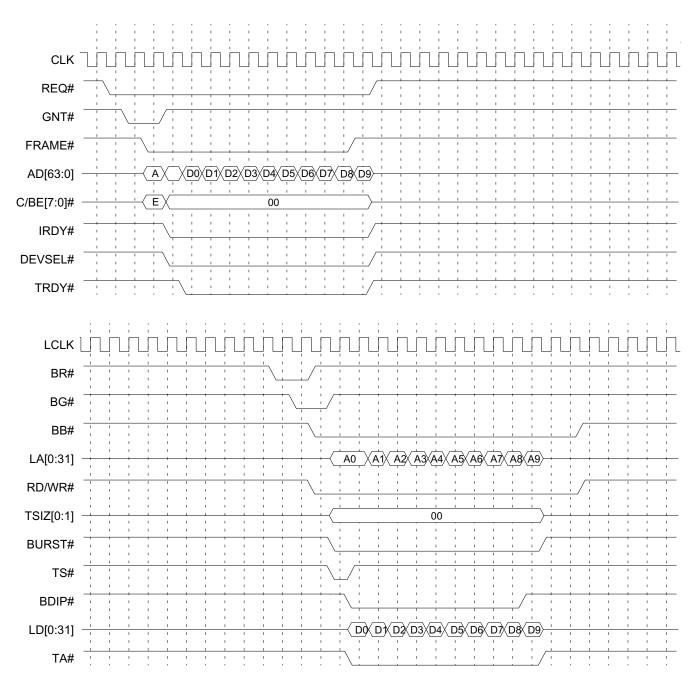

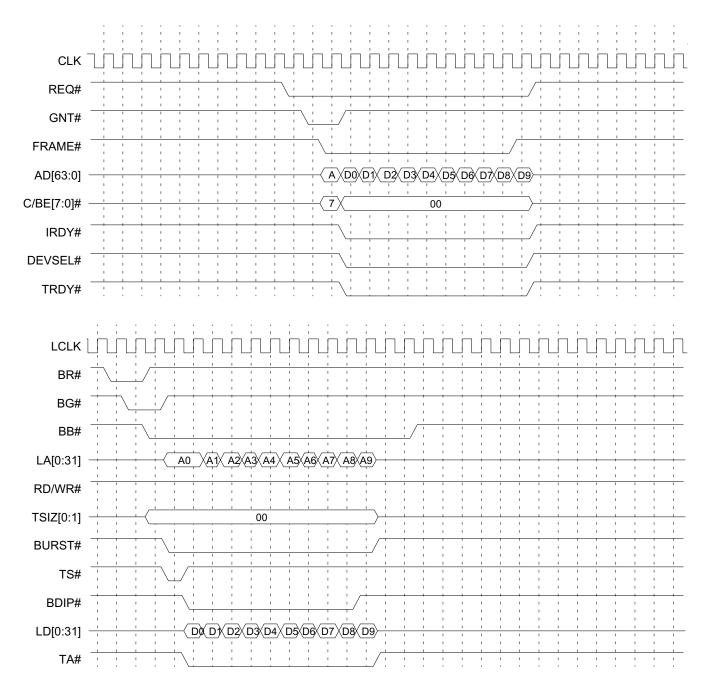

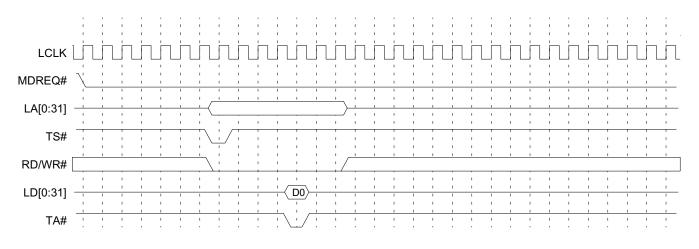

| 3.5. M Mode Functional Timing Diagrams       | 3-45 |

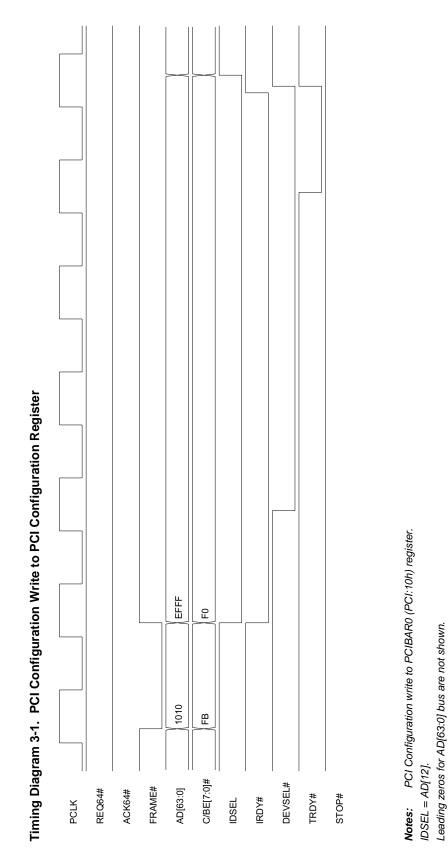

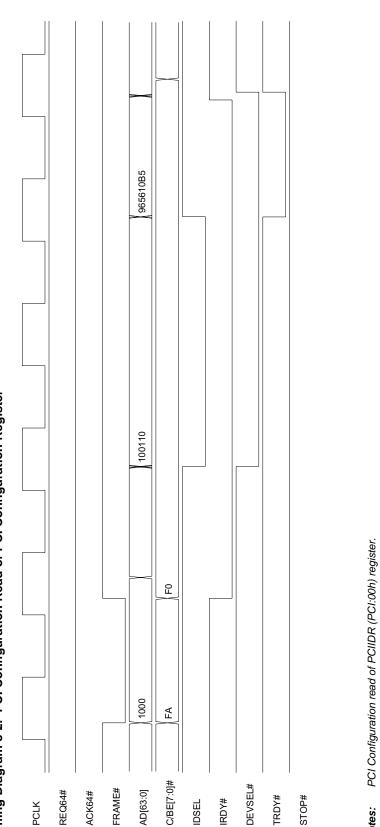

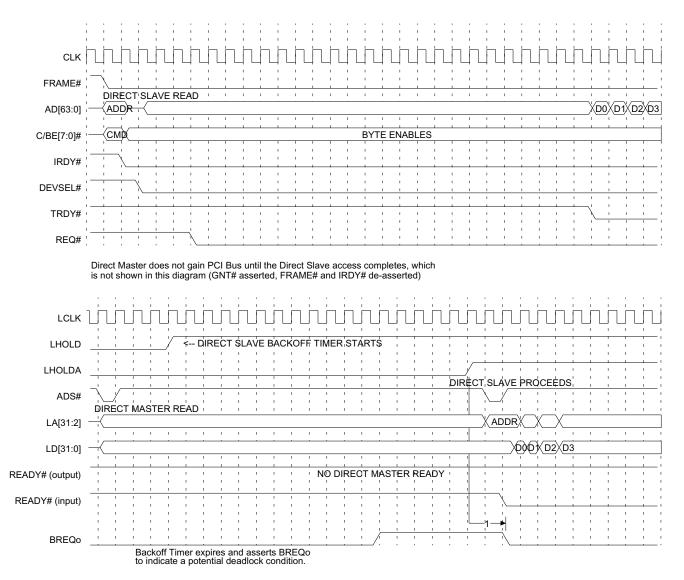

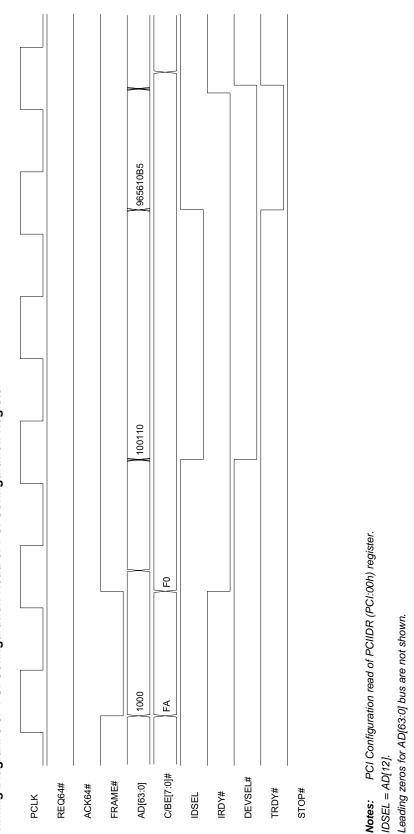

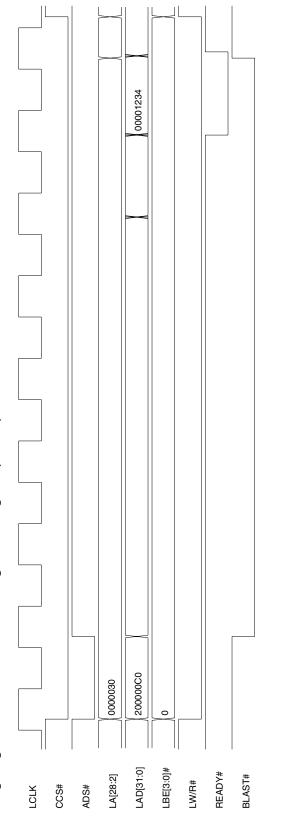

| 3.5.1. Configuration Timing Diagrams         | 3-46 |

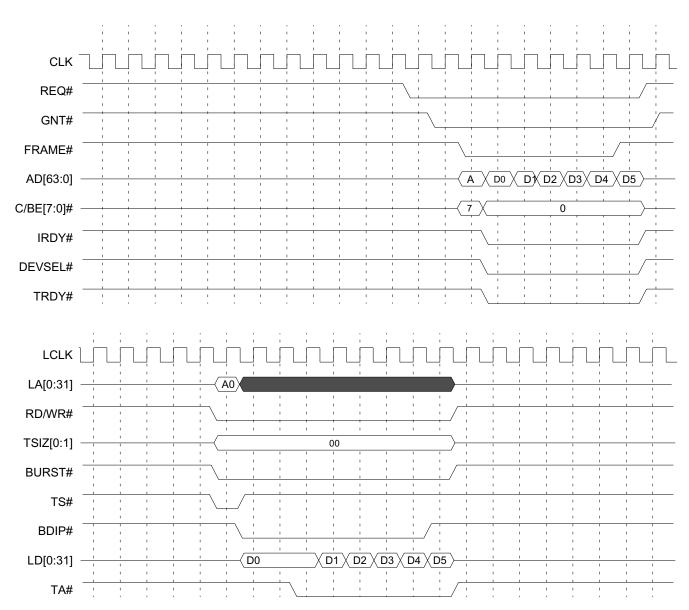

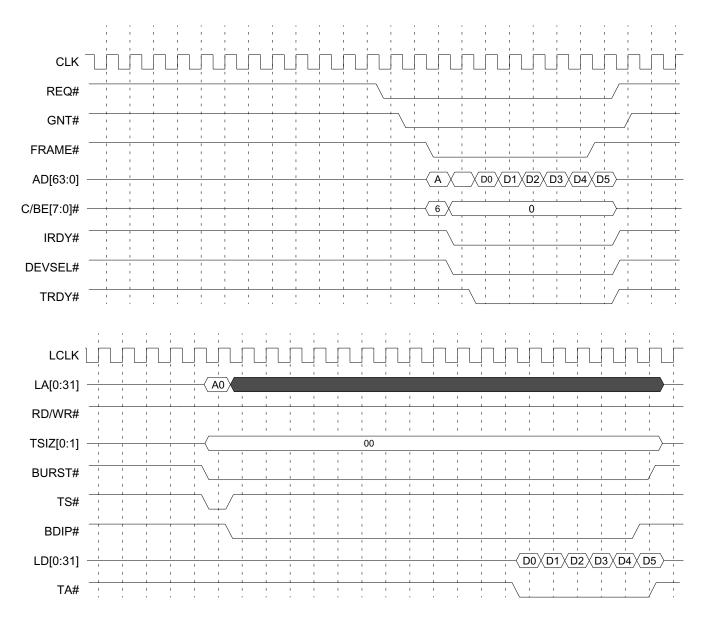

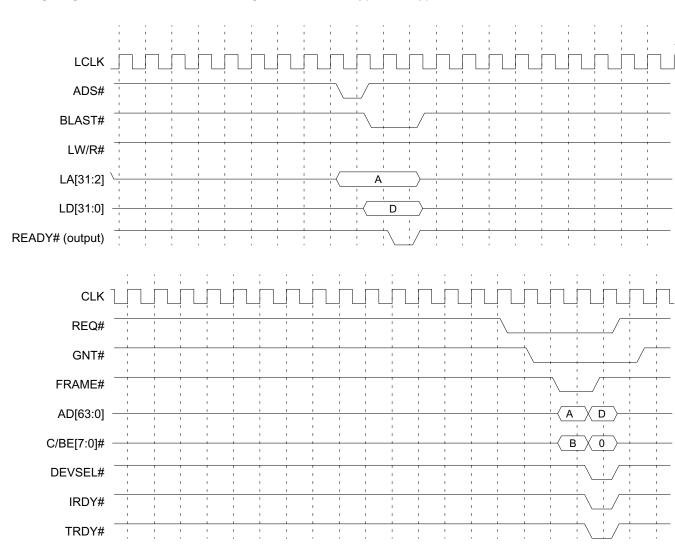

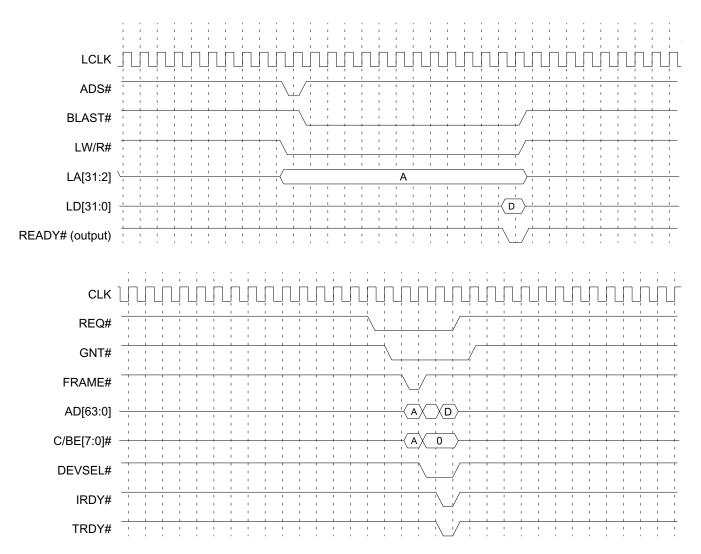

| 3.5.2. M Mode Direct Master Timing Diagrams  | 3-50 |

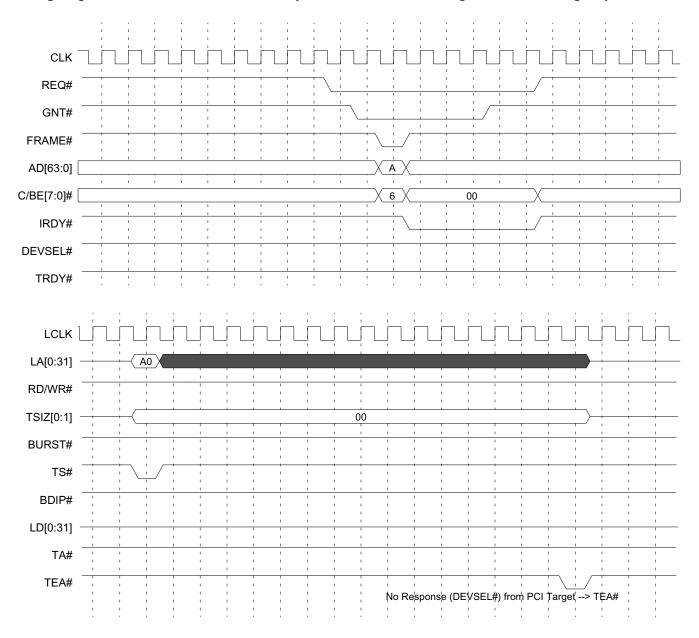

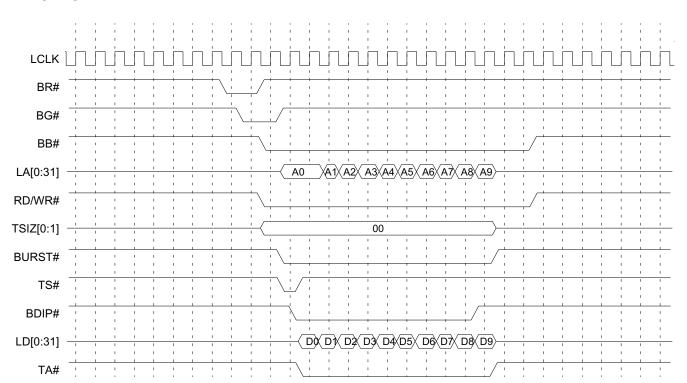

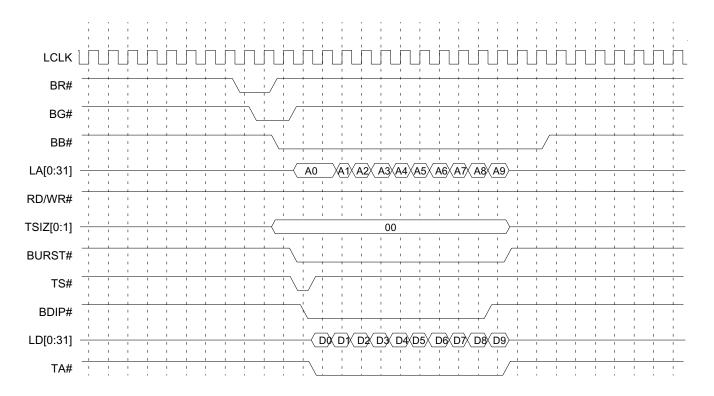

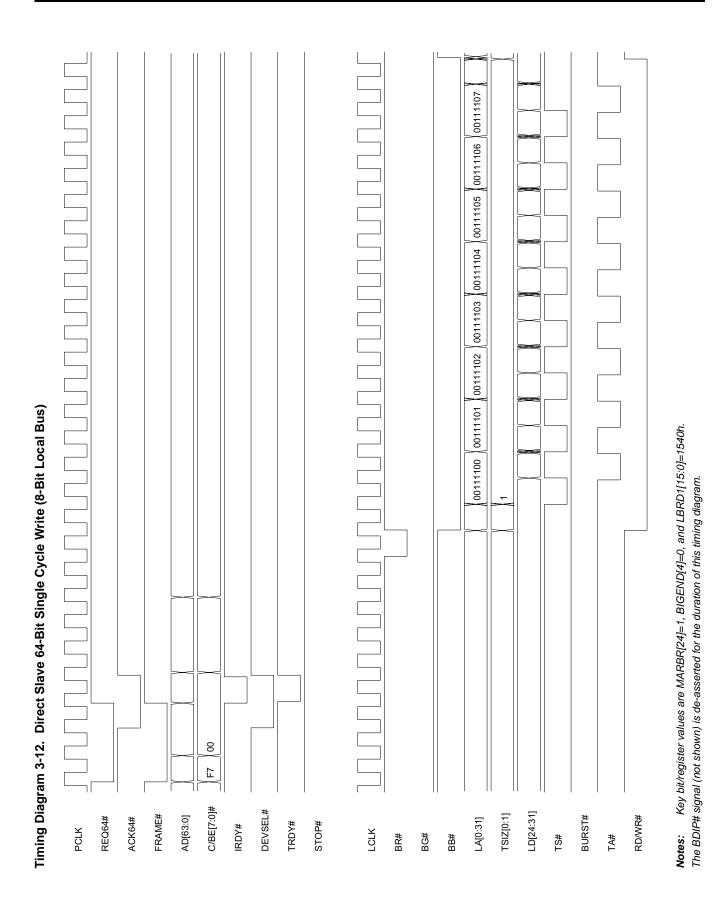

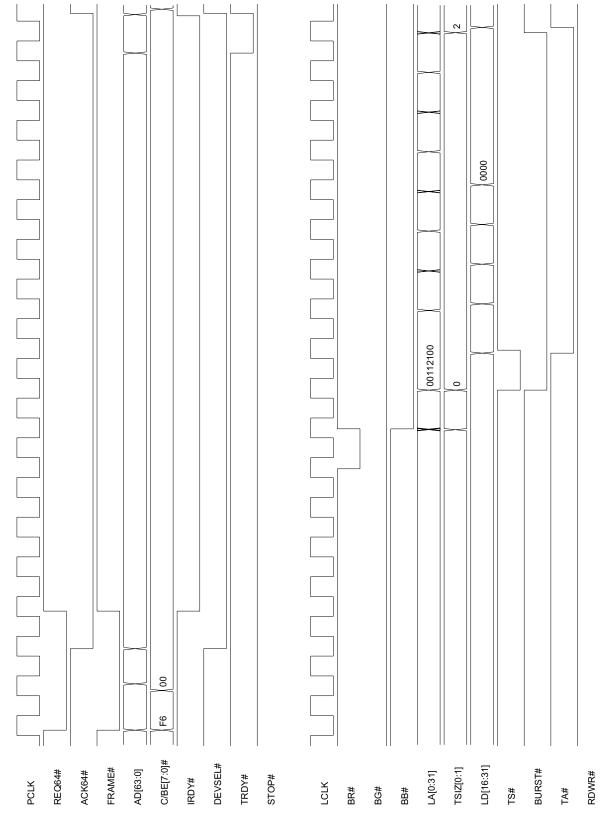

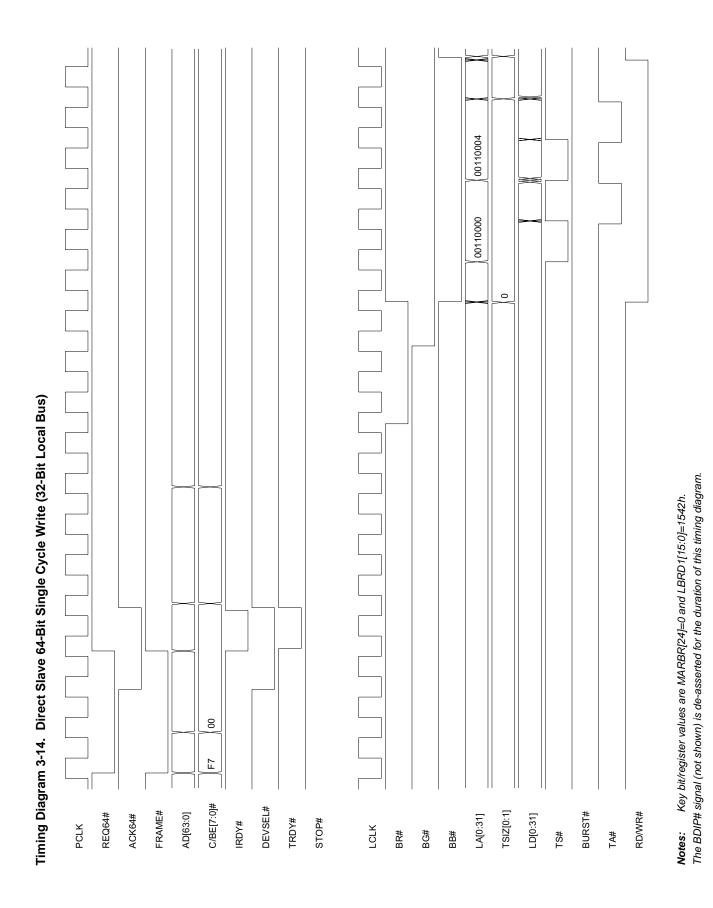

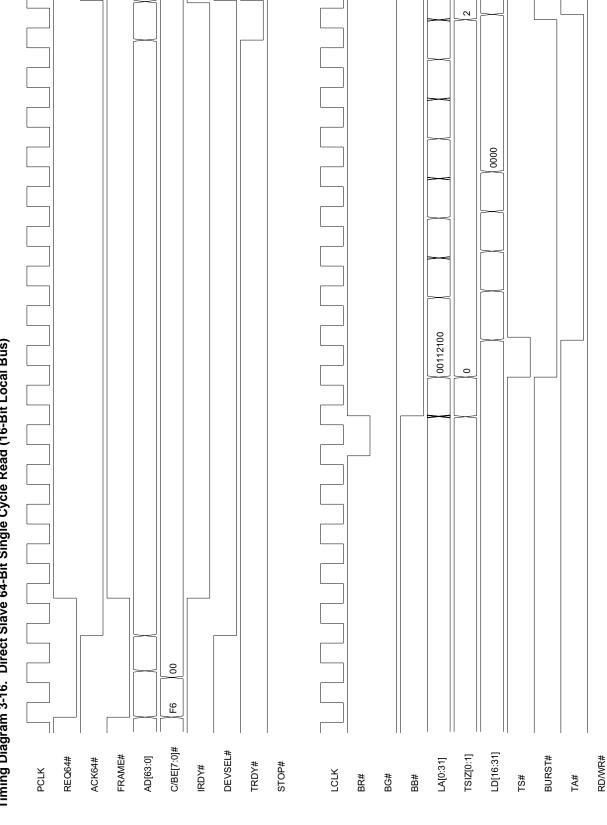

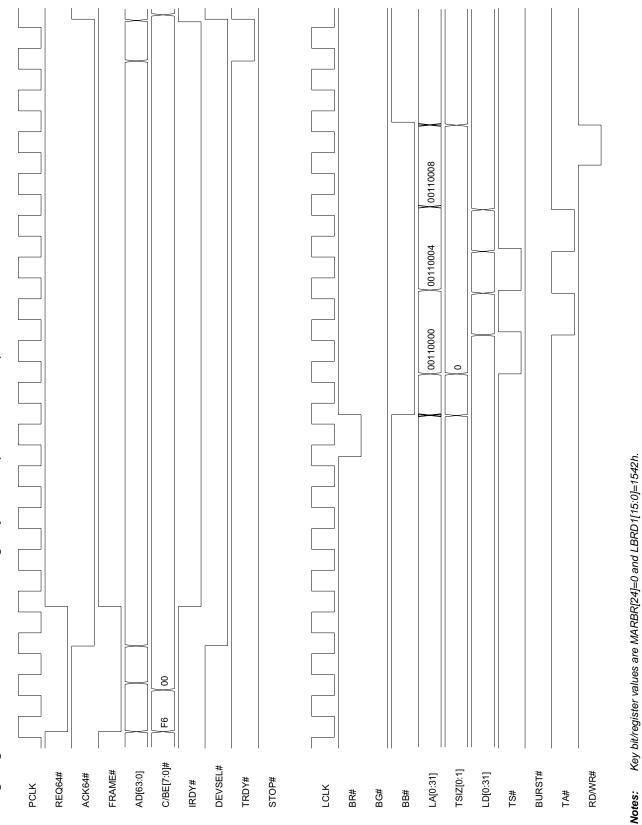

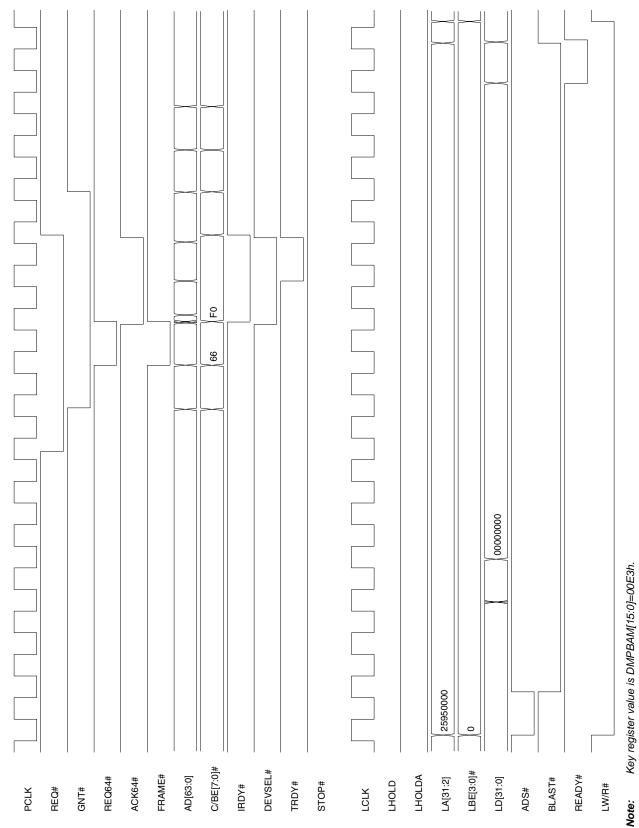

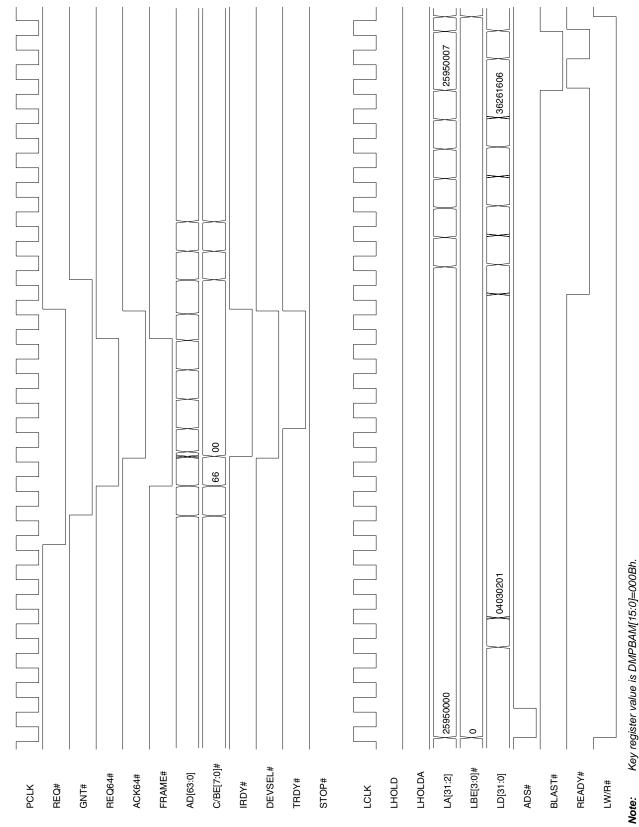

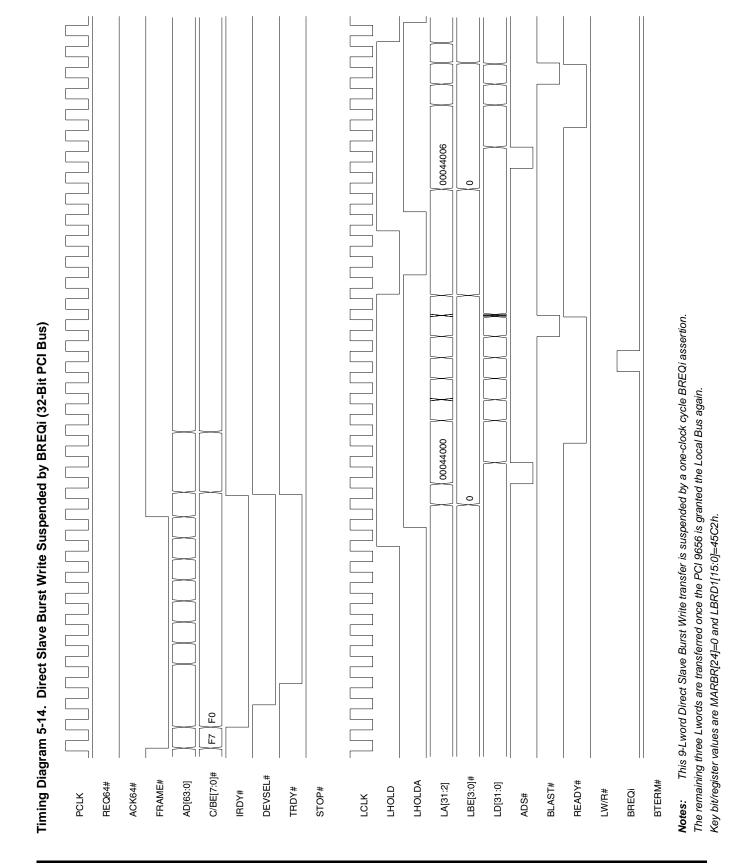

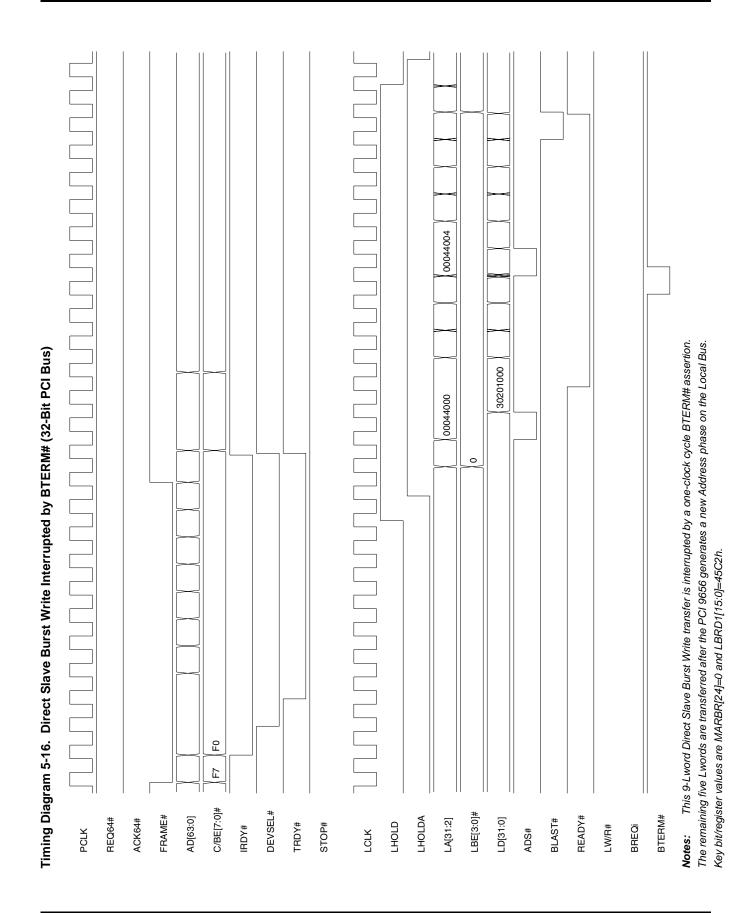

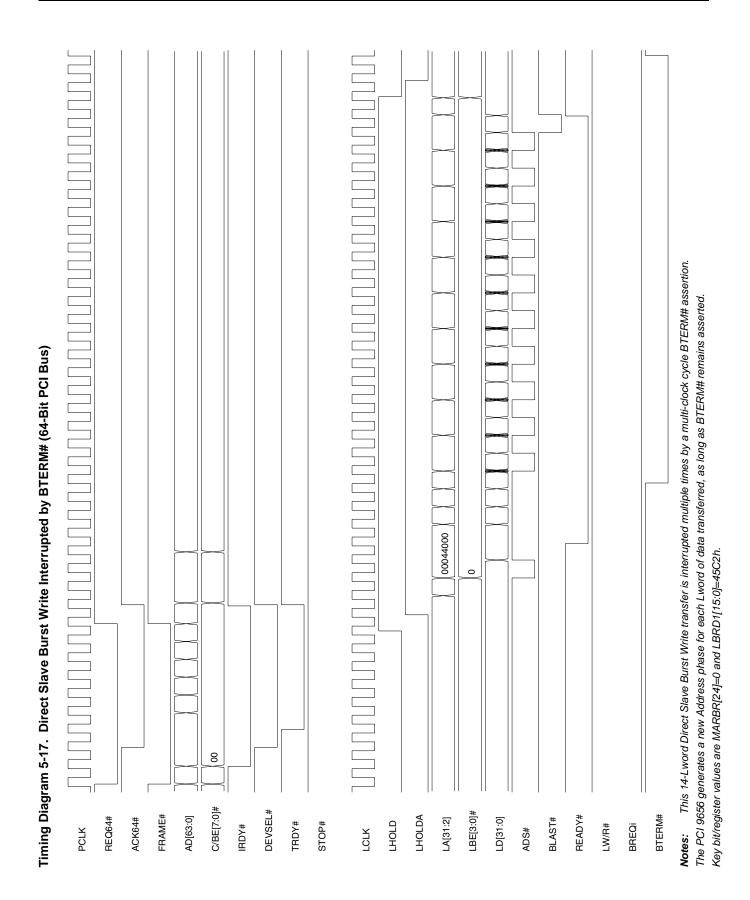

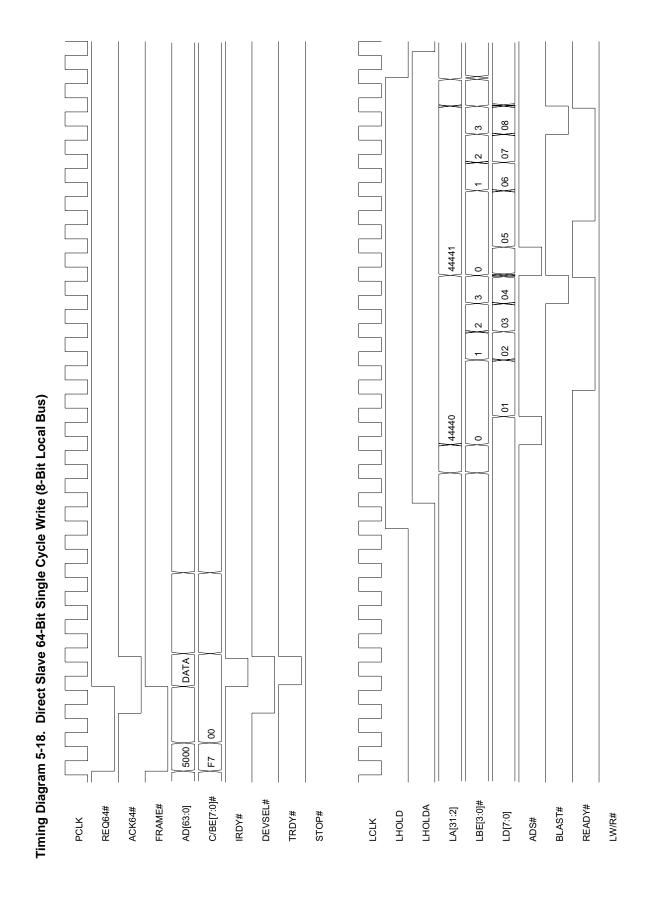

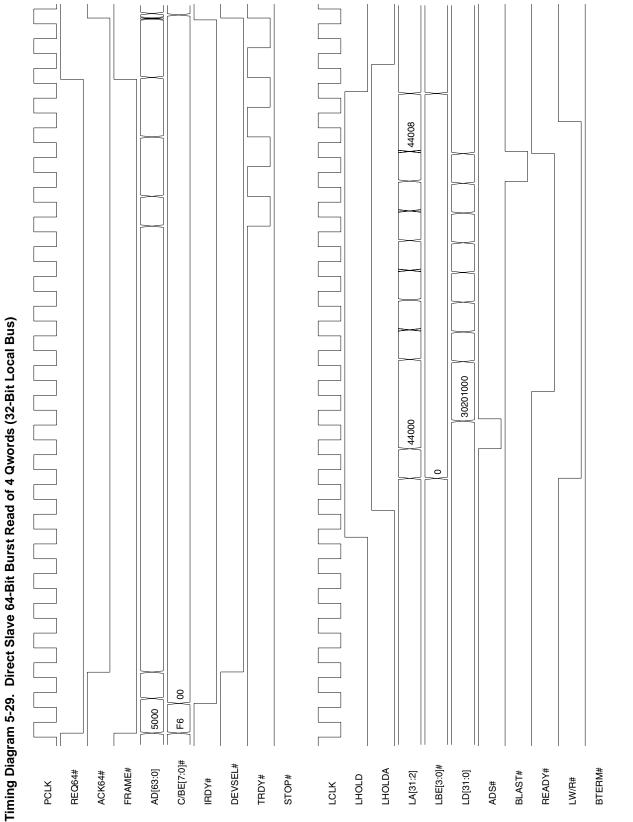

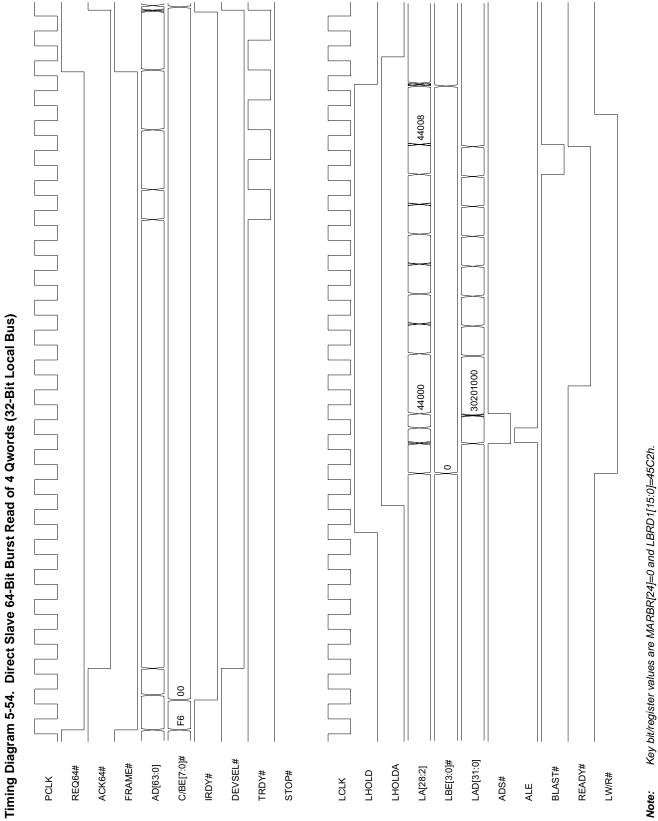

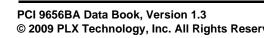

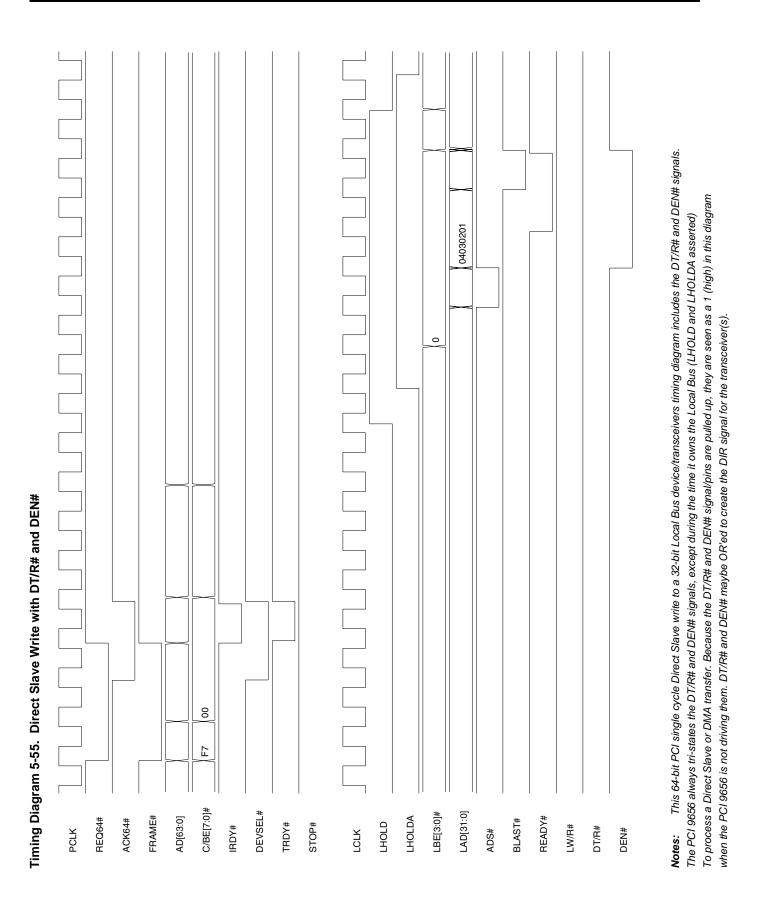

| 3.5.3. M Mode Direct Slave Timing Diagrams   | 3-55 |

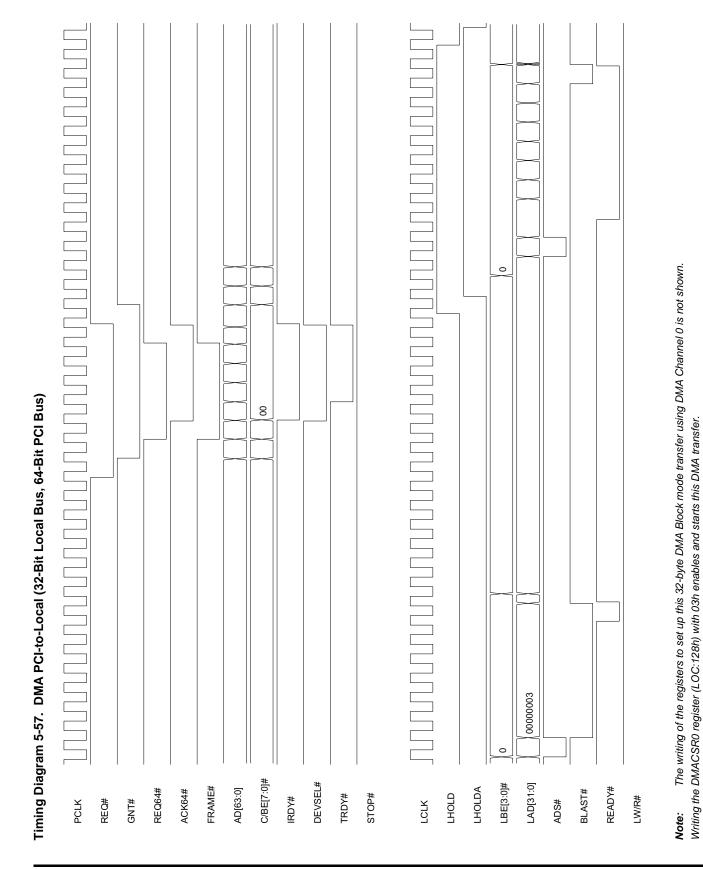

| 3.5.4. M Mode DMA Timing Diagrams            | 3-69 |

|                                              |      |

| 4. C and J Modes Bus Operation                         | . 4-1 |

|--------------------------------------------------------|-------|

| 4.1. PCI Bus Cycles                                    | 4-1   |

| 4.1.1. Direct Slave Command Codes                      |       |

| 4.1.2. PCI Master Command Codes                        |       |

| 4.1.2.1. DMA Master Command Codes                      |       |

| 4.1.2.2. Direct Local-to-PCI Command Codes.            |       |

| 4.1.3. PCI Arbitration                                 |       |

| 4.1.4. PCI Bus Wait States                             |       |

| 4.2. Local Bus Cycles                                  |       |

| 4.2.1. Local Bus Arbitration and BREQi                 |       |

| 4.2.1.1. Local Bus Arbitration Timing Diagram          |       |

| 4.2.2. Direct Master                                   |       |

| 4.2.3. Direct Slave                                    |       |

| 4.2.4. Wait State Control                              |       |

| 4.2.4.1. Local Bus Wait States.                        |       |

| 4.2.5. Data Transfer Modes                             |       |

| 4.2.5.1. Single Cycle Mode                             |       |

| 4.2.5.1.1. Partial Data Accesses                       |       |

| 4.2.5.2. Burst-4 Mode                                  |       |

| 4.2.5.2.1. Partial Data (<4 Bytes) Accesses            | 4-6   |

| 4.2.5.3. Continuous Burst Mode                         |       |

| 4.2.6. Recovery States (J Mode Only)                   |       |

| 4.2.7. Local Bus Read Accesses                         | 4-6   |

| 4.2.8. Local Bus Write Accesses                        | 4-7   |

| 4.2.9. Direct Slave Accesses to 8- or 16-Bit Local Bus | 4-7   |

| 4.2.10. Local Bus Data Parity                          | 4-7   |

| 4.3. Big Endian/Little Endian                          | 4-7   |

| 4.3.1. PCI Bus Data Bits Mapping onto Local Bus        | 4-7   |

| 4.3.2. Local Bus Big/Little Endian Mode Accesses       | 4-12  |

| 4.4. Serial EEPROM                                     | 4-12  |

| 4.4.1. PCI 9656 Initialization from Serial EEPROM      | 4-12  |

| 4.4.2. Local Initialization and PCI Bus Behavior       | 4-14  |

| 4.4.2.1. Long Serial EEPROM Load                       | 4-14  |

| 4.4.2.2. Extra Long Serial EEPROM Load.                | 4-14  |

| 4.4.3. Serial EEPROM Access                            |       |

| 4.4.4. Serial EEPROM Initialization Timing Diagram     | 4-18  |

| 4.5. Internal Register Access.                         |       |

| 4.5.1. PCI Bus Access to Internal Registers            | 4-20  |

| 4.5.1.1. New Capabilities Function Support.            | 4-21  |

| 4.5.2. Local Bus Access to Internal Registers          | 4-21  |

| 5. C and J Modes Functional Description                                          | . 5-1 |

|----------------------------------------------------------------------------------|-------|

| 5.1. Reset Operation                                                             | 5_1   |

| 5.1.1. Adapter Mode                                                              |       |

| 5.1.1.1. PCI Bus RST# Input                                                      |       |

| 5.1.1.2. JTAG Reset TRST# Input.                                                 |       |

|                                                                                  |       |

| 5.1.1.3. Software Reset                                                          |       |

| 5.1.1.4. Power Management Reset                                                  |       |

| 5.1.2. Host Mode                                                                 |       |

| 5.1.2.1. Local Reset.                                                            |       |

| 5.1.2.2. Software Reset                                                          |       |

| 5.1.2.3. Power Management Reset                                                  |       |

| 5.2. PCI 9656 Initialization                                                     |       |

| 5.3. Response to FIFO Full or Empty                                              |       |

| 5.4. Direct Data Transfer Modes                                                  |       |

| 5.4.1. Direct Master Operation (Local Master-to-PCI Slave)                       |       |

| 5.4.1.1. Direct Master Memory and I/O Decode                                     |       |

| 5.4.1.2. Direct Master FIFOs                                                     |       |

| 5.4.1.3. Direct Master Memory Access                                             | 5-6   |

| 5.4.1.3.1. Direct Master Writes                                                  |       |

| 5.4.1.3.2. Direct Master Reads                                                   | 5-7   |

| 5.4.1.4. Direct Master I/O                                                       | 5-7   |

| 5.4.1.5. Direct Master Delayed Write Mode                                        | 5-8   |

| 5.4.1.6. Direct Master Read Ahead Mode                                           | 5-8   |

| 5.4.1.7. Direct Master Configuration (PCI Type 0 or Type 1 Configuration Cycles) | 5-10  |

| 5.4.1.7.1. Direct Master Configuration Cycle Example                             | 5-10  |

| 5.4.1.8. Direct Master PCI Dual Address Cycles                                   |       |

| 5.4.1.9. PCI Master/Target Abort.                                                |       |

| 5.4.1.10. Direct Master Memory Write and Invalidate                              |       |

| 5.4.1.11. Direct Master Write FIFO Programmable Almost Full, DMPAF Flag          |       |

| 5.4.2. Direct Slave Operation (PCI Master-to-Local Bus Access)                   |       |

| 5.4.2.1. Direct Slave Writes                                                     |       |

| 5.4.2.2. Direct Slave Reads                                                      |       |

| 5.4.2.3. Direct Slave Lock                                                       |       |

| 5.4.2.4. PCI Compliance Enable                                                   |       |

| 5.4.2.4.1. Direct Slave Delayed Read Mode                                        |       |

| 5.4.2.4.2. 2 <sup>15</sup> PCI Clock Timeout                                     | 5-16  |

| 5.4.2.4.3. <i>PCI r</i> 2.2 16- and 8-Clock Rule                                 |       |

| 5.4.2.5. Direct Slave Read Ahead Mode                                            |       |

| 5.4.2.6. Direct Slave Read Arlead Mode                                           |       |

| 5.4.2.7. Direct Slave Delayed Withe Mode                                         |       |

| 5.4.2.7. Direct Slave Local Bus READ 1# Timeout Mode                             |       |

|                                                                                  |       |

| 5.4.2.9. Direct Slave PCI-to-Local Address Mapping.                              |       |

| 5.4.2.9.1. Direct Slave Local Bus Initialization                                 |       |

| 5.4.2.9.2. Direct Slave PCI Initialization                                       |       |

| 5.4.2.9.3. Direct Slave PCI Initialization Example                               |       |

| 5.4.2.9.4. Direct Slave Byte Enables (C Mode)                                    |       |

| 5.4.2.9.5. Direct Slave Byte Enables (J Mode)                                    |       |

| 5.4.2.10. Direct Slave Priority                                                  |       |

| 5.4.3. Deadlock Conditions                                                       |       |

| 5.4.3.1. Backoff                                                                 |       |

| 5.4.3.1.1. Software/Hardware Solution for Systems without Backoff Capability     |       |

| 5.4.3.1.2. Preempt Solution                                                      |       |

| 5.4.3.2. Software Solutions to Deadlock                                          |       |

| 5.4.4. DMA Operation                                                             |       |

| 5.4.4.1. DMA PCI Dual Address Cycles                                             |       |

| 5.4.4.2. DMA Block Mode                                                          |       |

| 5.4.4.2.1. DMA Block Mode PCI Dual Address Cycles                                | 5-26  |

|                                                                                  |       |

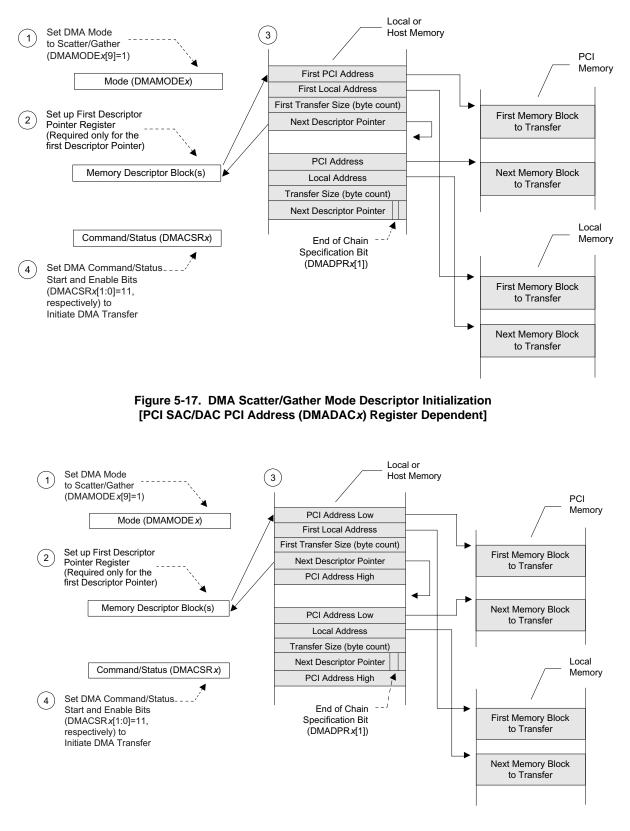

| 5.4.4.3. DMA Scatter/Gather Mode                         | 5-26  |

|----------------------------------------------------------|-------|

| 5.4.4.3.1. DMA Scatter/Gather PCI Dual Address Cycle     | 5-27  |

| 5.4.4.3.2. DMA Clear Count Mode                          |       |

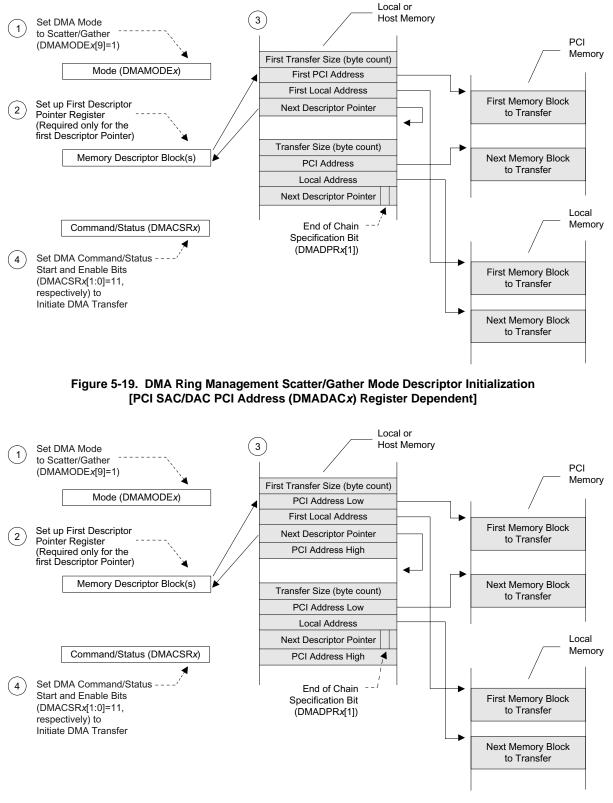

| 5.4.4.3.3. DMA Ring Management (Valid Mode)              |       |

| 5.4.4.4. DMA Memory Write and Invalidate                 |       |

| 5.4.4.5. DMA Abort                                       |       |

| 5.4.4.6. DMA Channel Priority                            |       |

| 5.4.4.7. DMA Channel x Interrupts                        |       |

| 5.4.4.8. DMA Data Transfers                              |       |

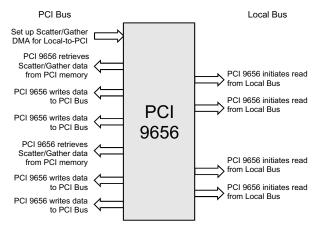

| 5.4.4.8.1. Local-to-PCI Bus DMA Transfer                 |       |

| 5.4.4.8.2. PCI-to-Local Bus DMA Transfer                 |       |

| 5.4.4.9. DMA Unaligned Transfers                         |       |

| 5.4.4.10. DMA Demand Mode, Channel x                     |       |

| 5.4.4.10.1. Fast/Slow Terminate Mode                     |       |

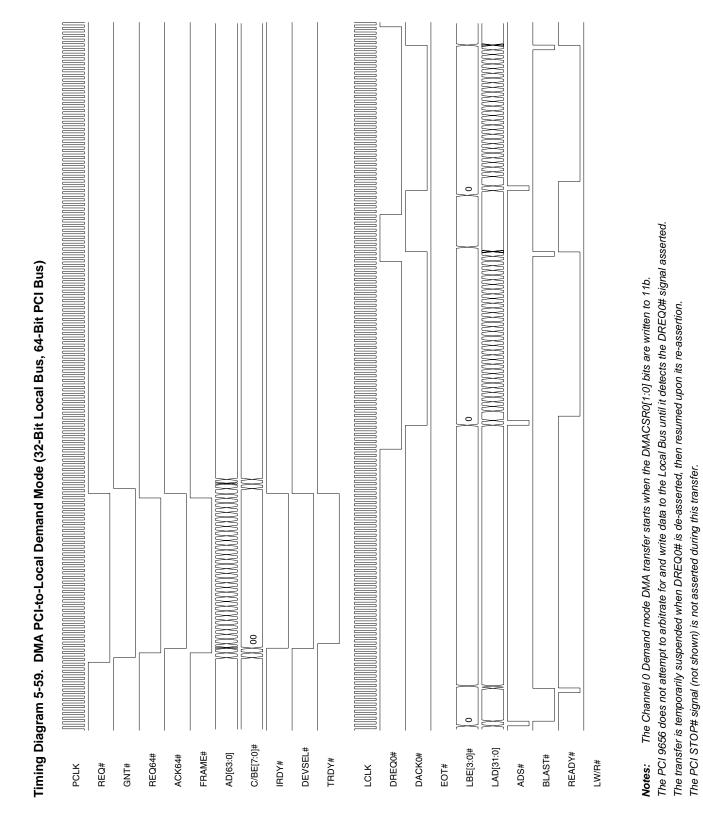

| 5.4.4.10.2. PCI-to-Local DMA Demand Mode                 |       |

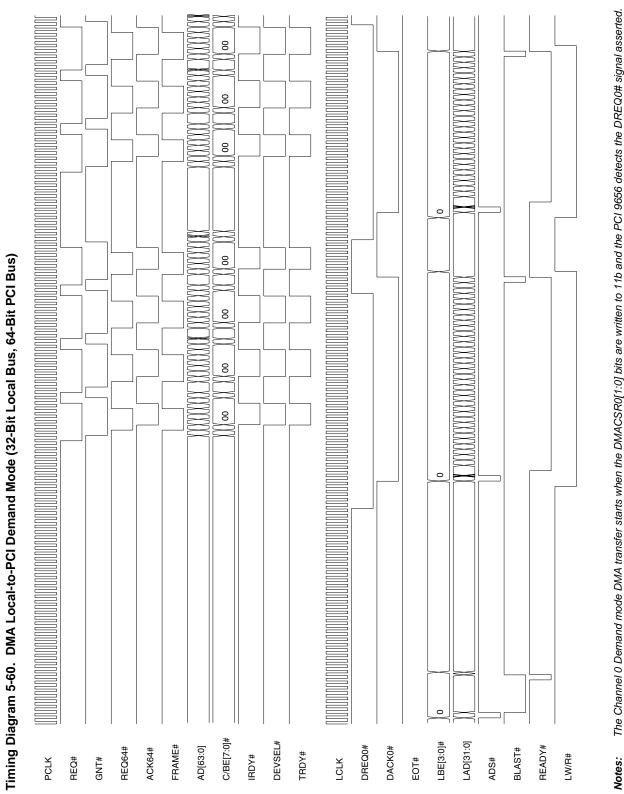

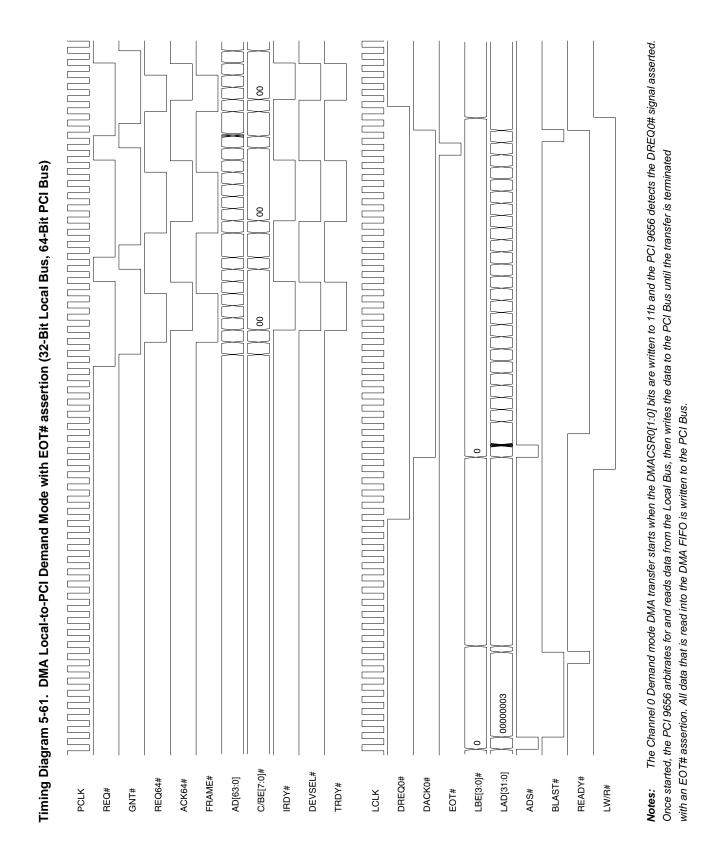

| 5.4.4.10.3. Local-to-PCI DMA Demand Mode                 |       |

| 5.4.4.11. End of Transfer (EOT#) Input                   |       |

| 5.4.4.12. DMA Arbitration                                |       |

| 5.4.4.13. Local Bus DMA Priority                         |       |

| 5.4.4.14. Local Bus Latency and Pause Timers             |       |

| 5.4.4.15. DMA FIFO Programmable Threshold                |       |

| 5.4.4.16. DMA PCI Master/Target Abort                    |       |

| 5.5. C and J Modes Functional Timing Diagrams            |       |

| 5.5.1. Configuration Timing Diagrams                     |       |

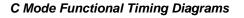

| 5.6. C Mode Functional Timing Diagrams                   |       |

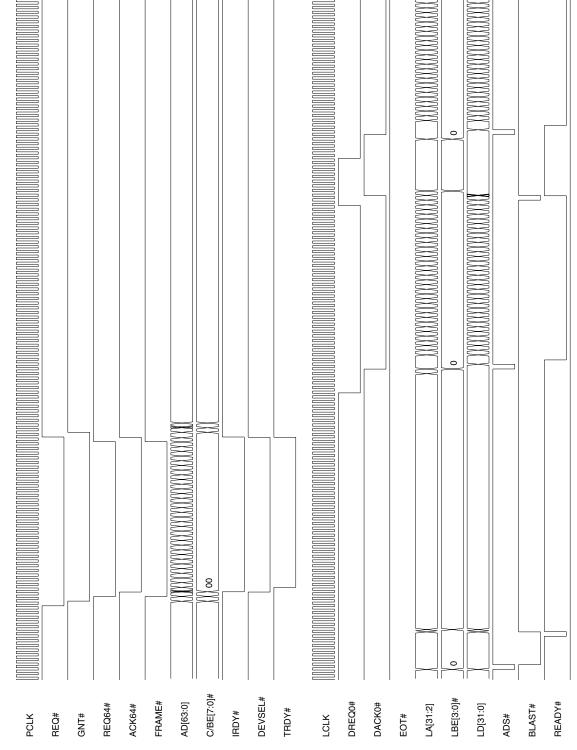

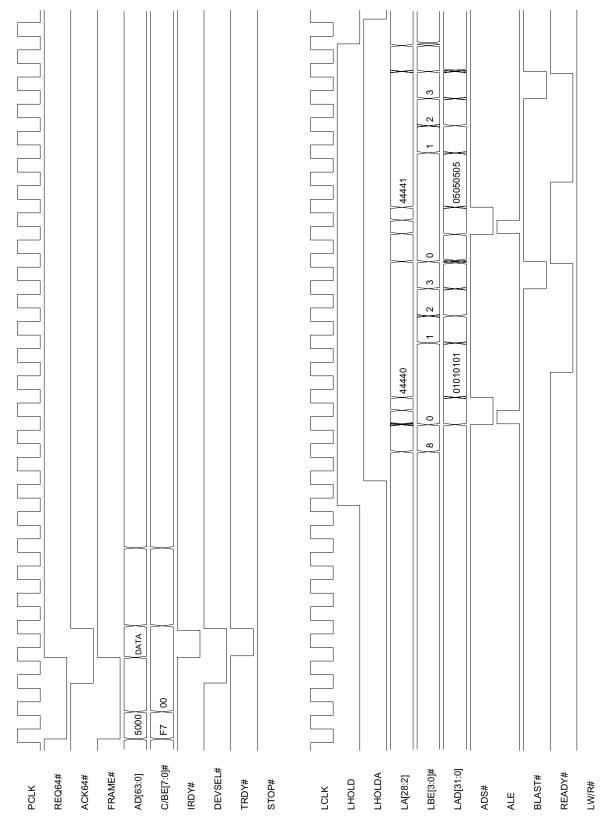

| 5.6.1. C Mode Direct Master Timing Diagrams              |       |

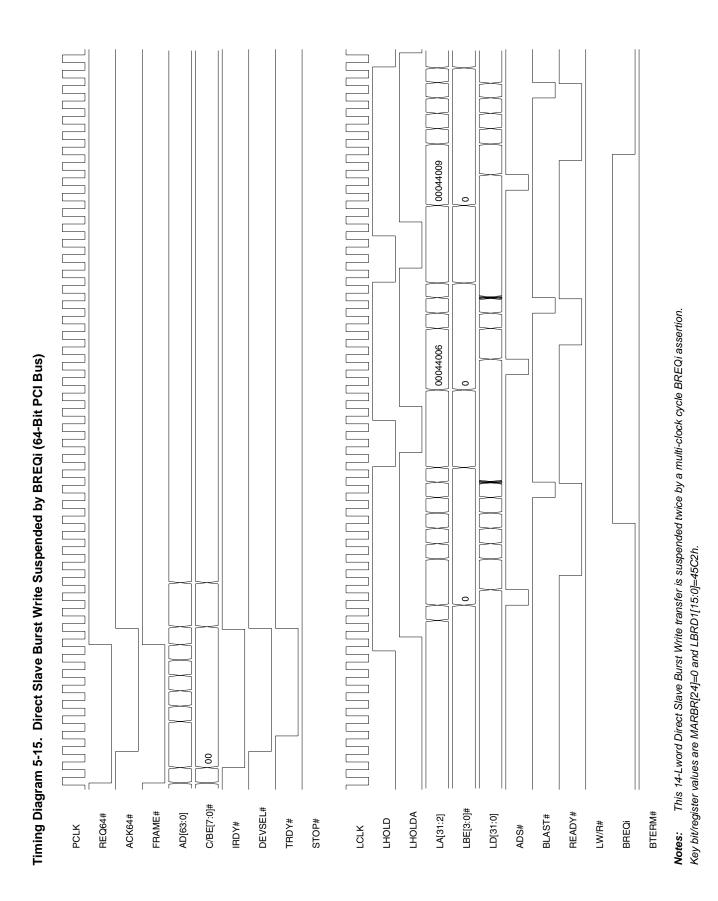

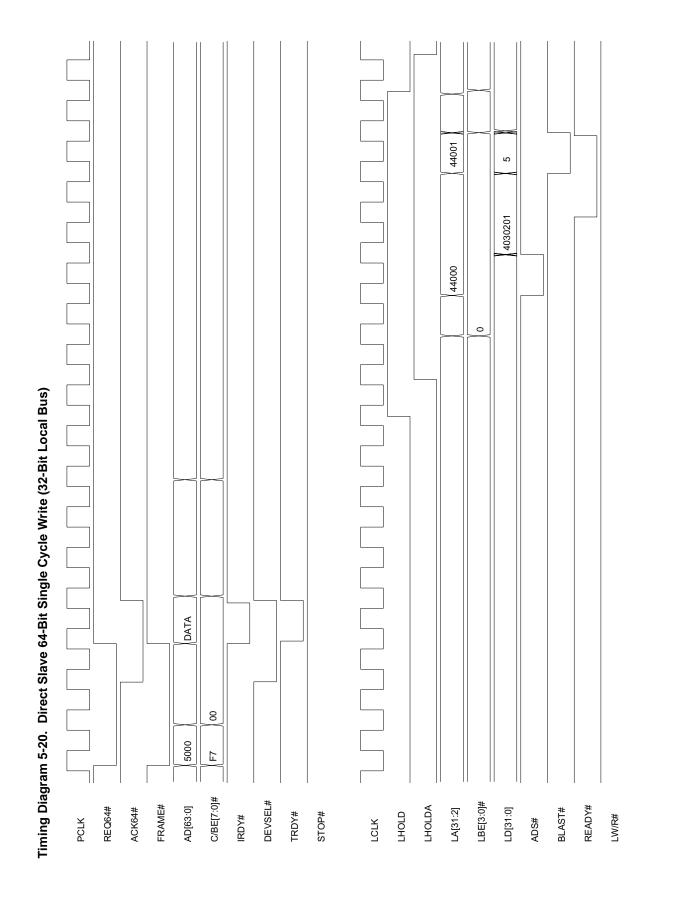

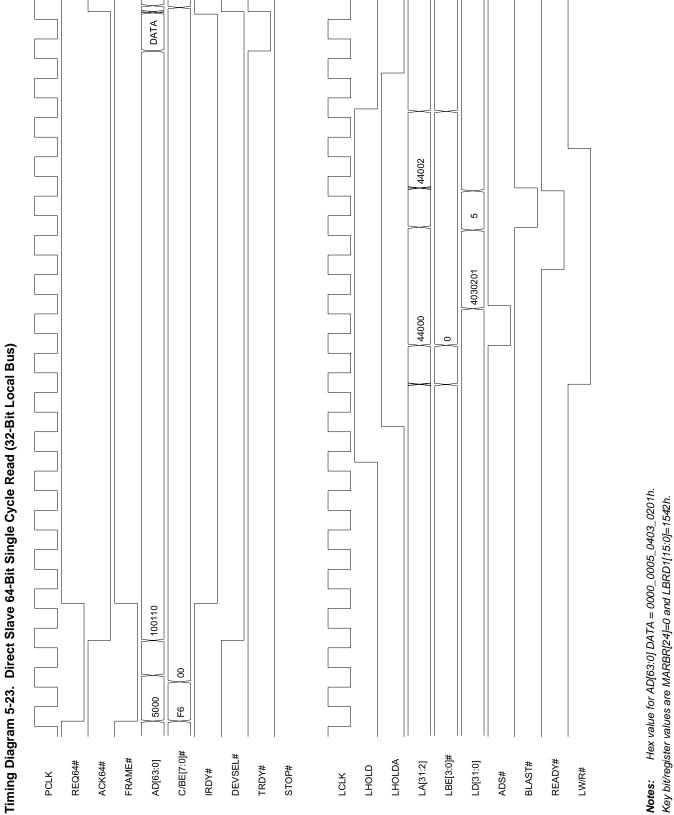

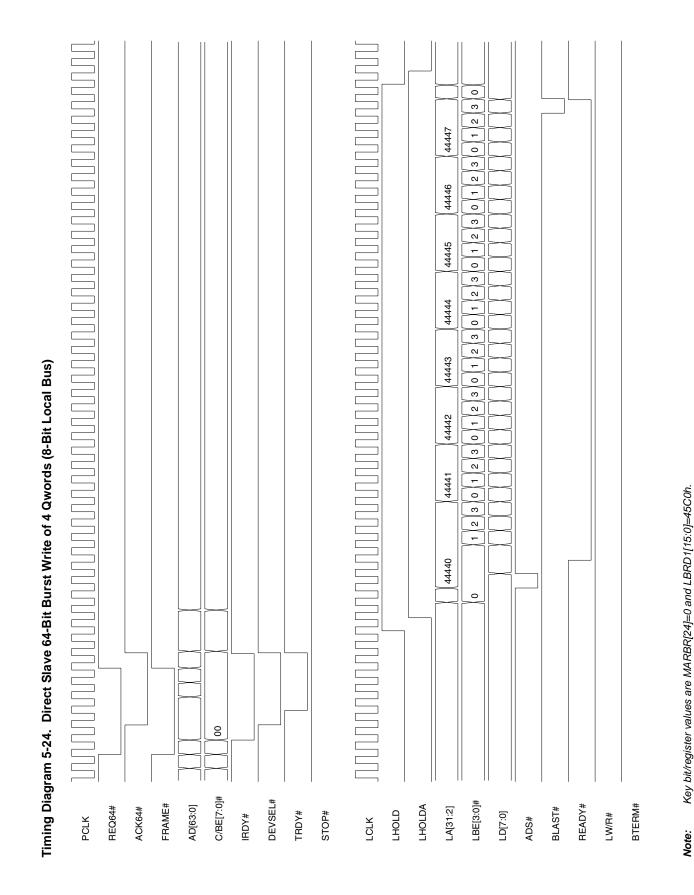

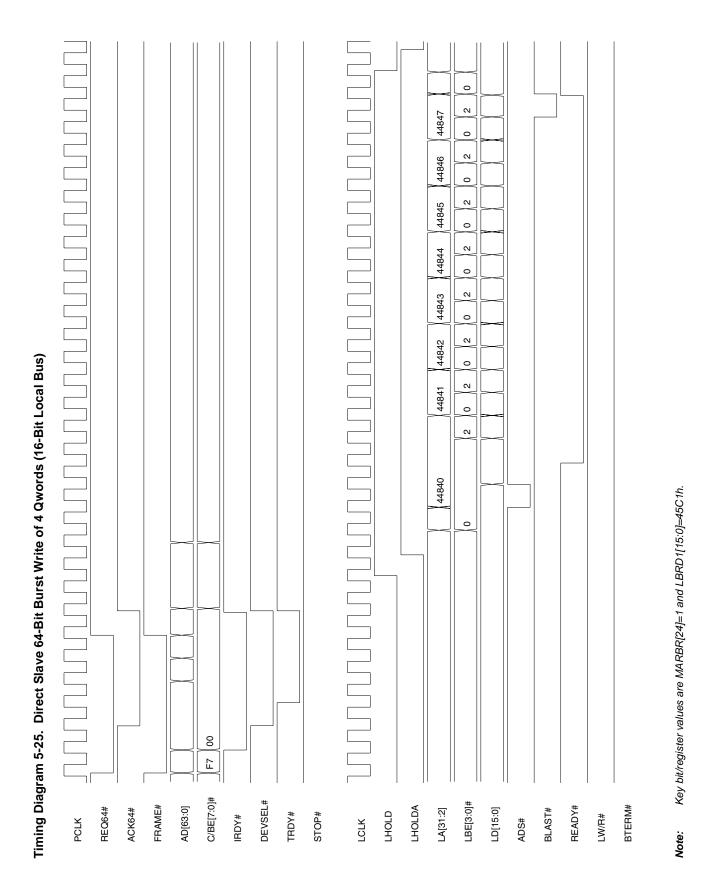

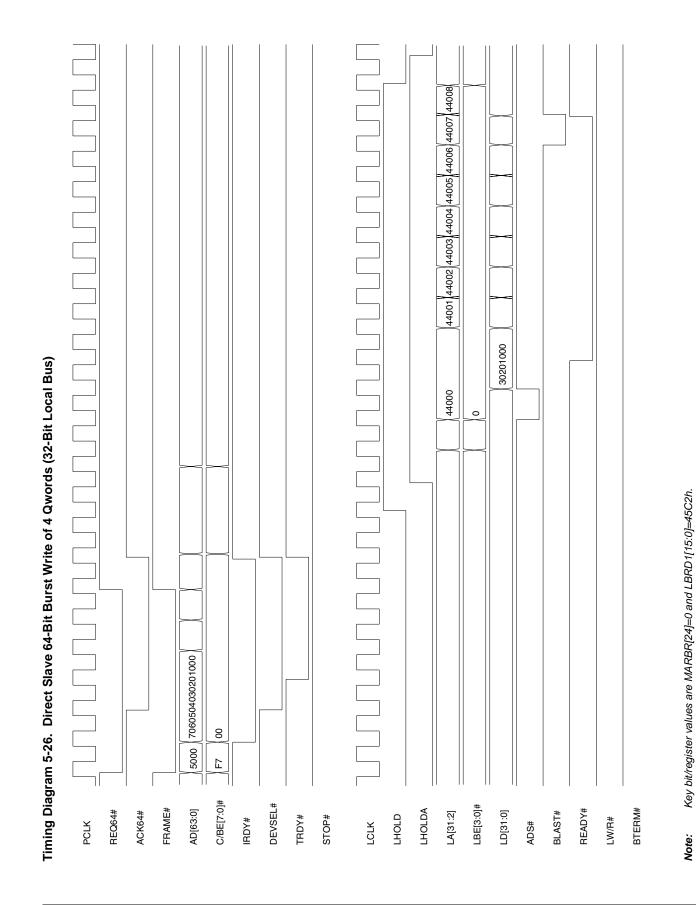

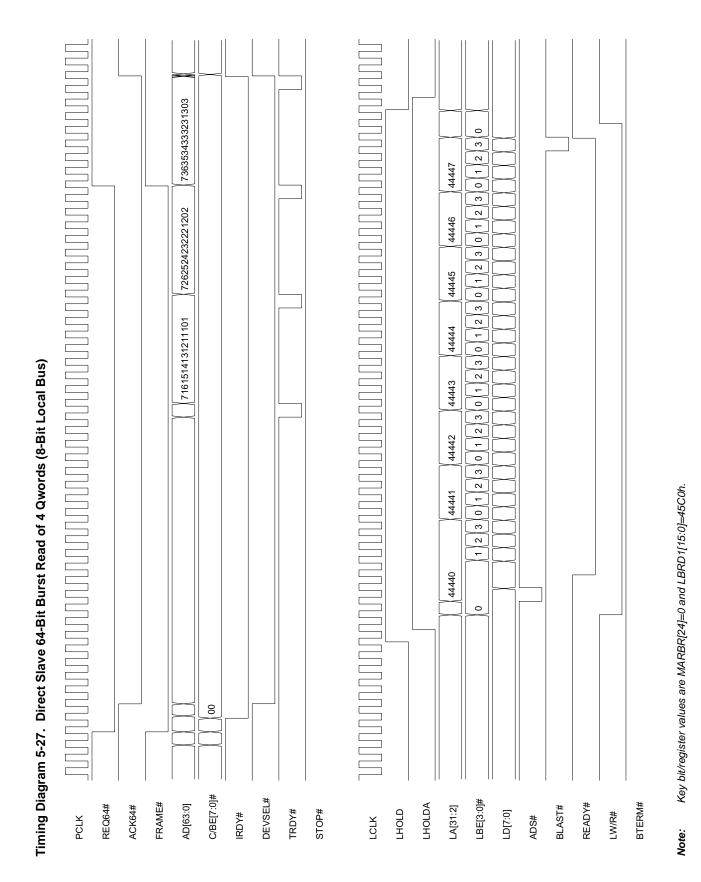

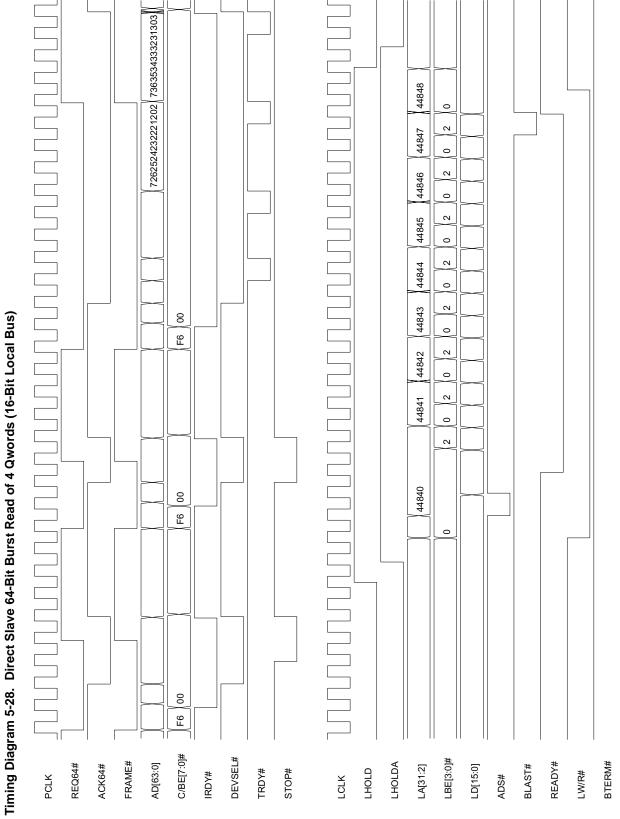

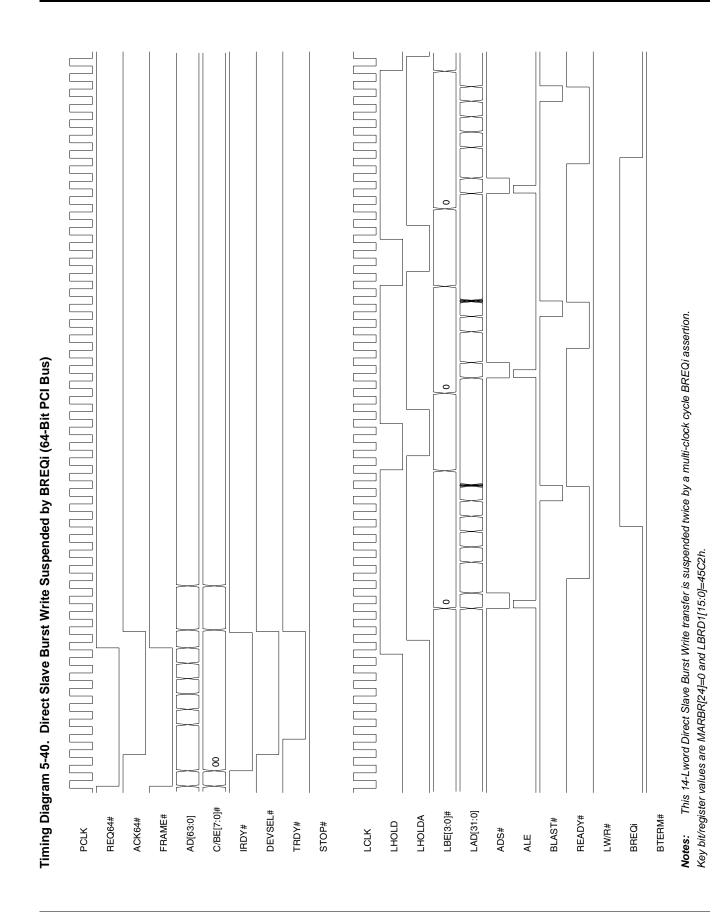

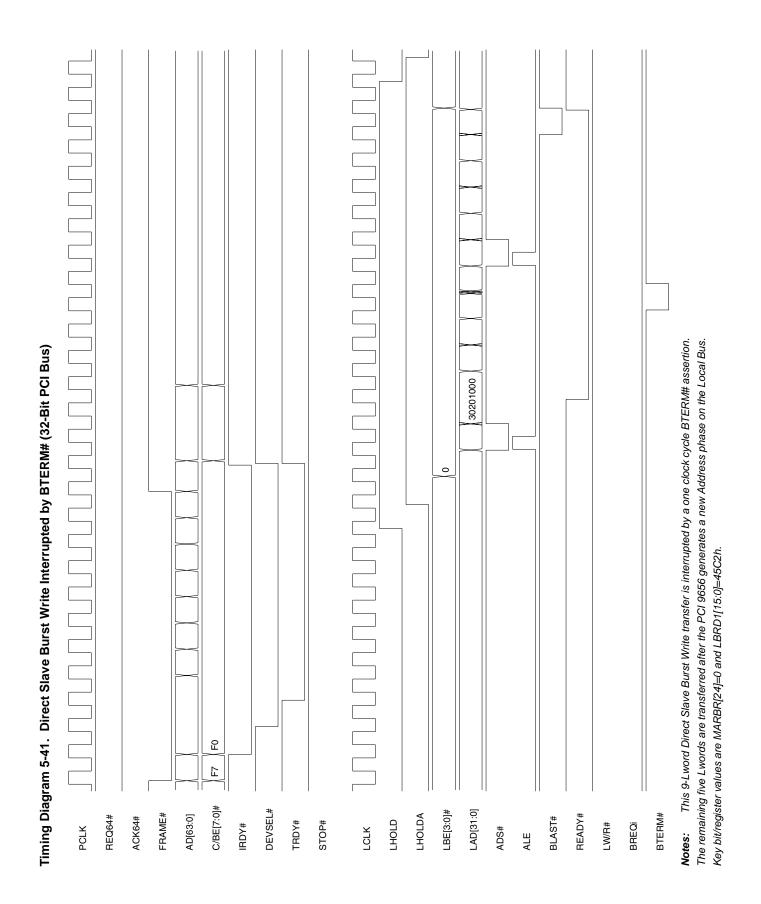

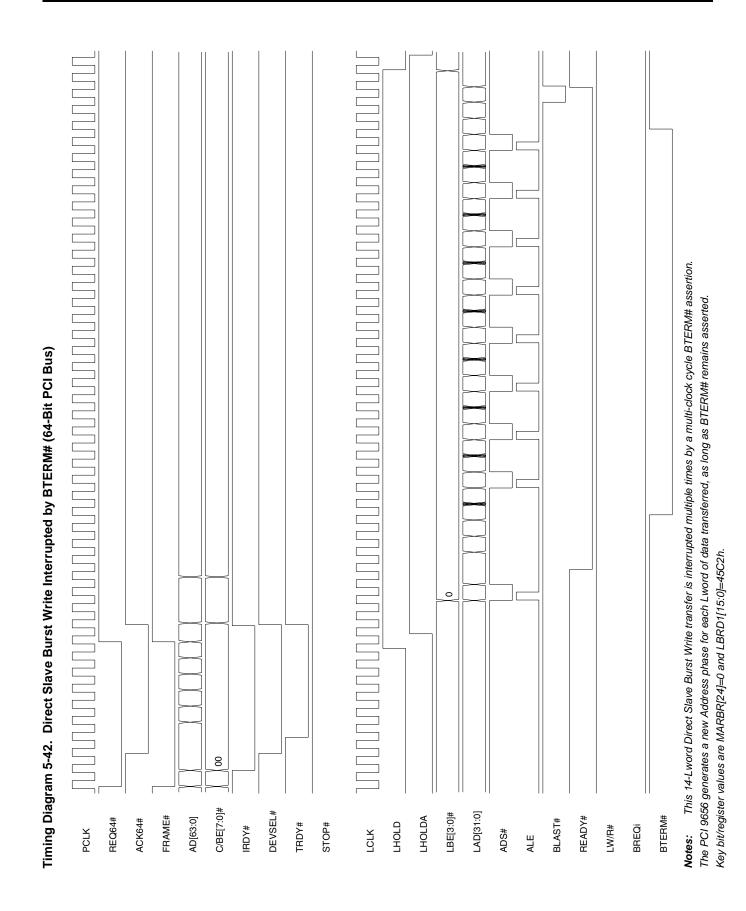

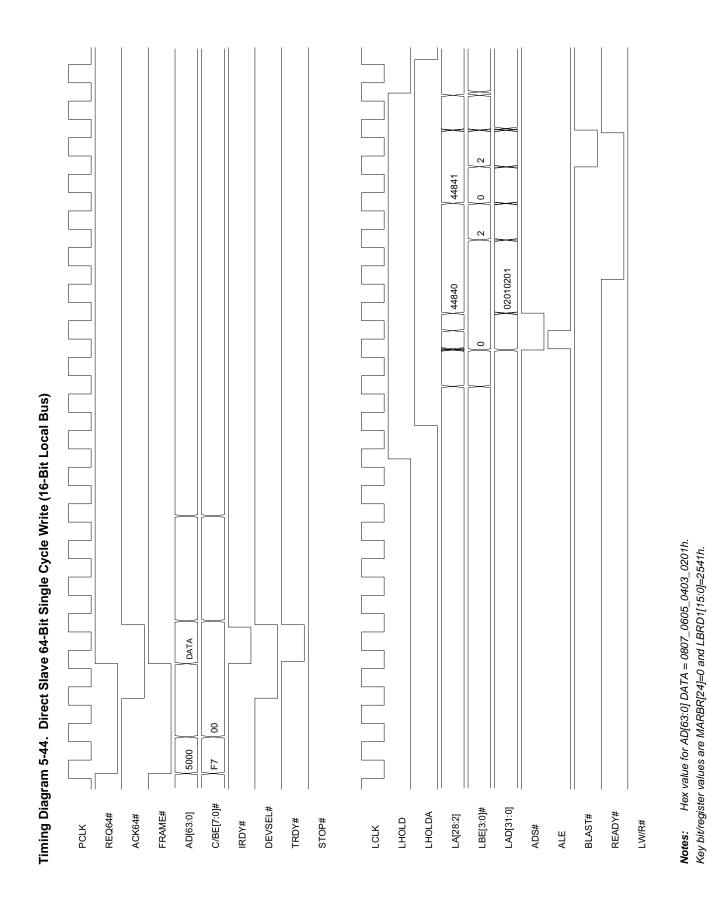

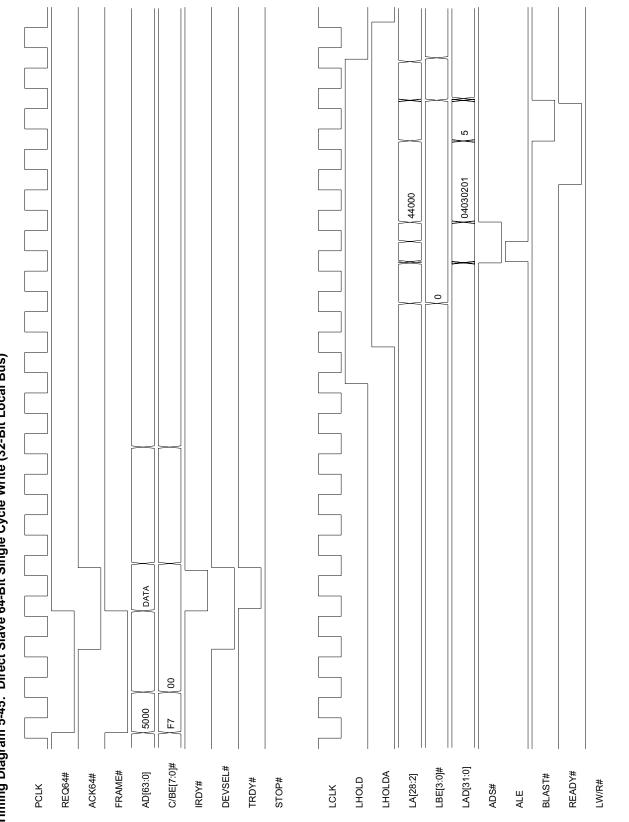

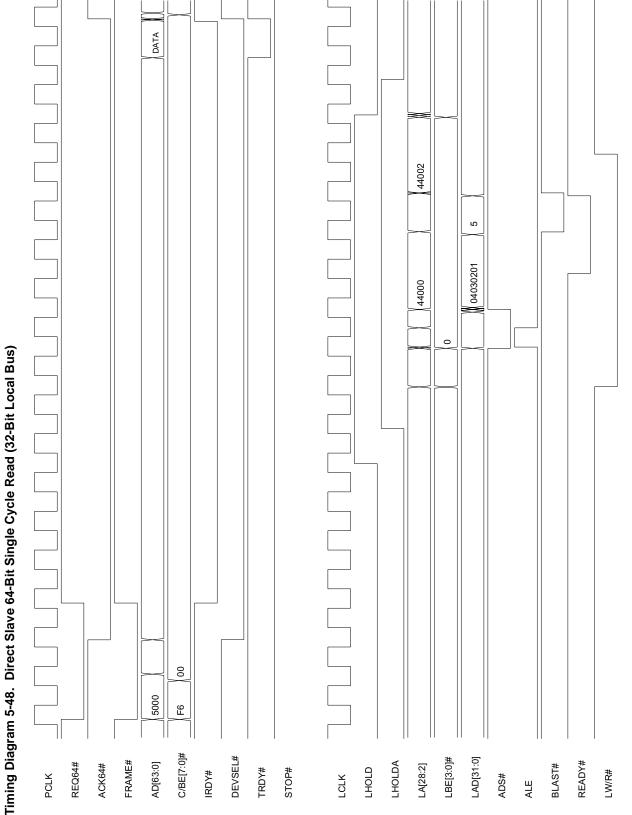

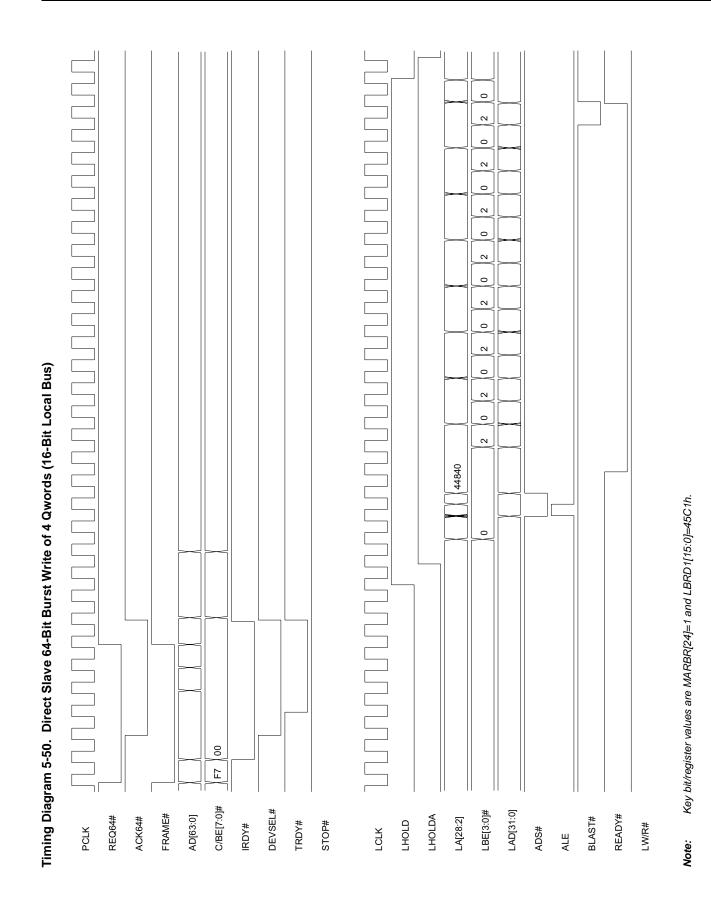

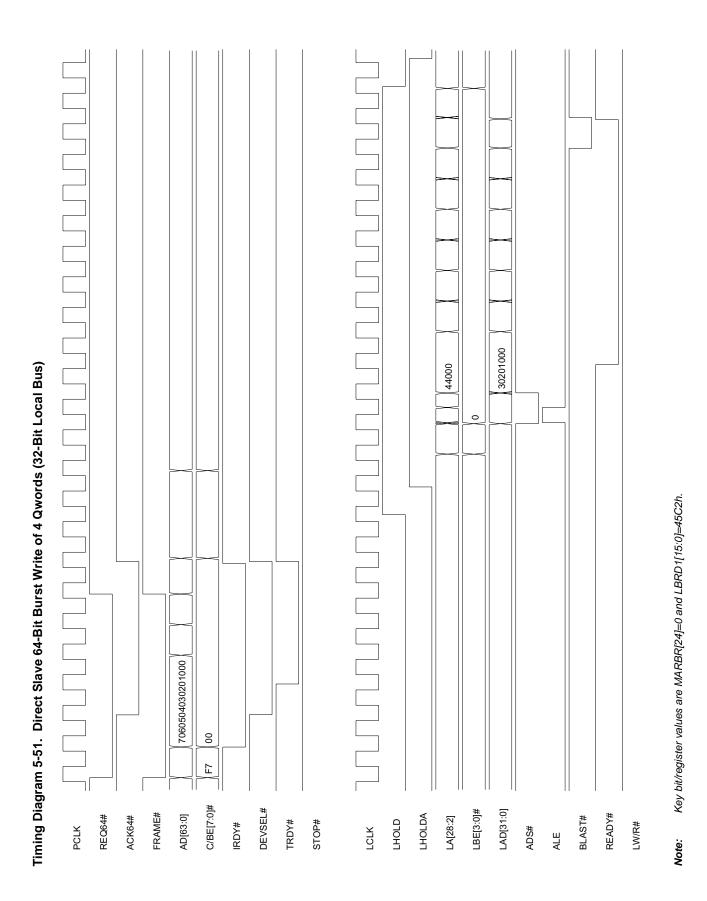

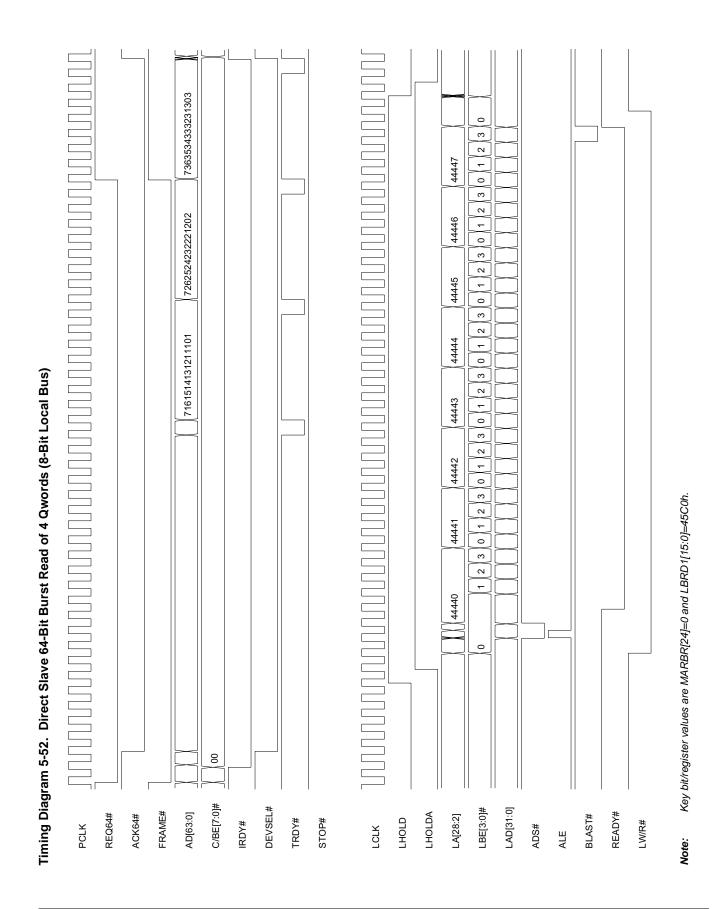

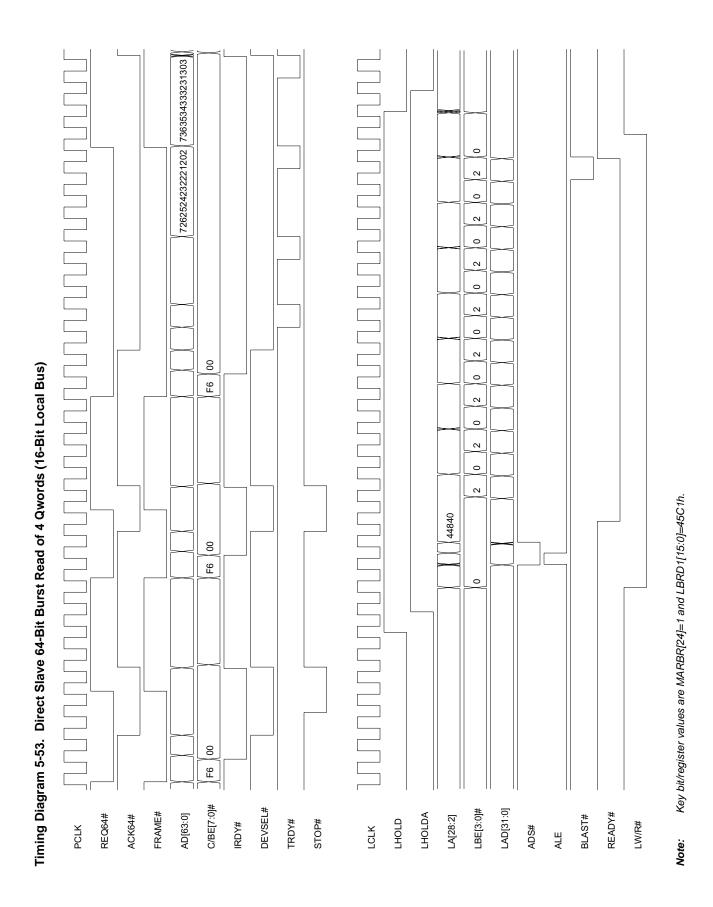

| 5.6.2. C Mode Direct Slave Timing Diagrams               |       |

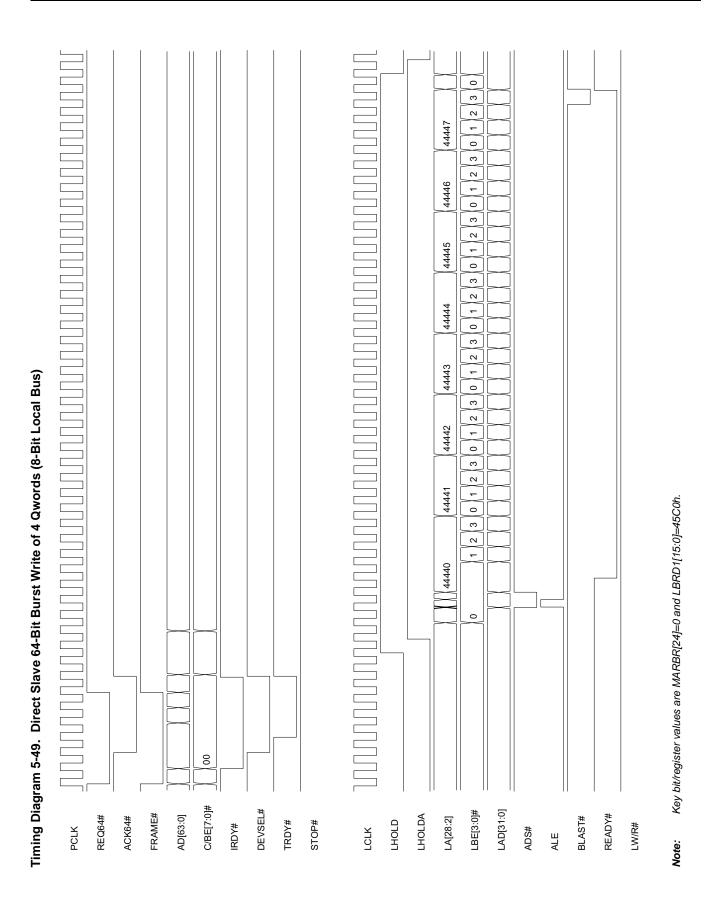

| 5.6.3. C Mode DMA Timing Diagrams                        |       |

| 5.7. J Mode Functional Timing Diagrams                   |       |

| 5.7.1. J Mode Direct Master Timing Diagrams              |       |

| 5.7.2. J Mode Direct Slave Timing Diagrams               |       |

| 5.7.3. J Mode DMA Timing Diagrams                        | 5-98  |

|                                                          |       |

| 6. Interrupts, User I/O, and IDDQEN#                     | 6-1   |

|                                                          | ••••• |

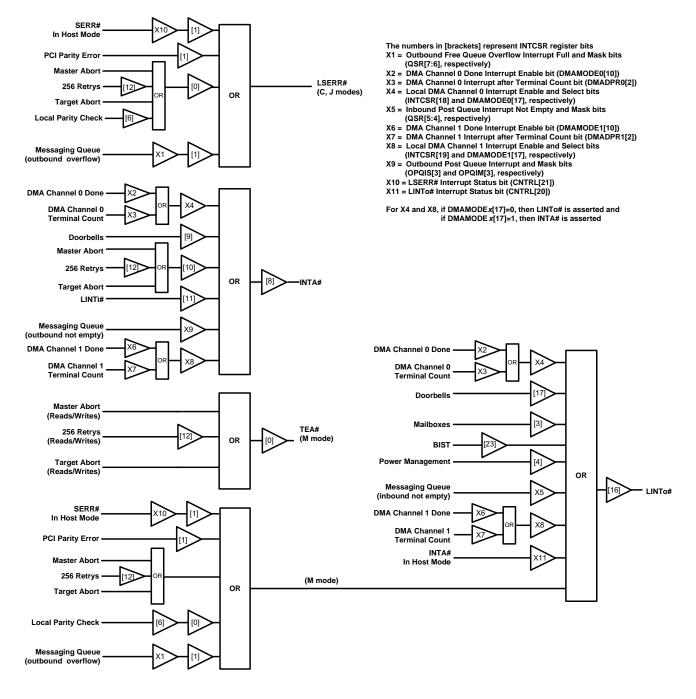

| 6.1. Interrupts.                                         | 6-1   |

| 6.1.1. PCI Interrupts (INTA#)                            | 6-2   |

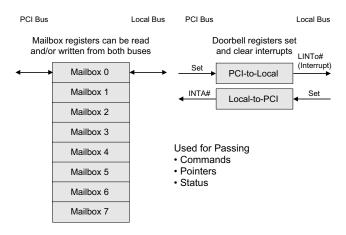

| 6.1.2. Local Interrupt Input (LINTi#)                    | 6-2   |

| 6.1.3. Local Interrupt Output (LINTo#)                   |       |

| 6.1.4. PCI Master/Target Abort Interrupt                 |       |

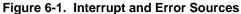

| 6.1.5. Mailbox Registers                                 |       |

| 6.1.6. Doorbell Registers                                |       |

| 6.1.6.1. Local-to-PCI Doorbell Interrupt                 |       |

| 6.1.6.1.1. M Mode Local-to-PCI Doorbell Interrupt        |       |

| 6.1.6.1.2. C and J Modes Local-to-PCI Doorbell Interrupt |       |

| 6.1.6.2. PCI-to-Local Doorbell Interrupt                 |       |

| 6.1.7. Built-In Self-Test Interrupt (BIST)               |       |

| 6.1.8. DMA Channel x Interrupts                          |       |

| 6.1.9. All Modes PCI SERR# (PCI NMI)                     |       |

| 6.1.10. M Mode PCI SERR#                                 |       |

| 6.1.11. All Modes PCI PERR# (PCI Parity Error)           |       |

| 6.1.12. M Mode Local Bus TEA# Signal                     |       |

| 6.1.13. C and J Modes Local LSERR# (Local NMI)           |       |

| 6.1.14. Interrupt Timing Diagram                         | 6-7   |

6.2. User I/O

6-8

6.3. IDDQEN# Multi-Function Shared Pin – Power-On Function.

6-8

| 7. Intelligent I/O (I <sub>2</sub> O)                      | 7-1   |

|------------------------------------------------------------|-------|

| 7.1. I <sub>2</sub> O-Compatible Messaging Unit            |       |

| 7.1.2. Outbound Messages                                   |       |

| 7.1.3. I <sub>2</sub> O Pointer Management                 |       |

| 7.1.4. Inbound Free List FIFO                              |       |

| 7.1.6. Outbound Post Queue FIFO                            |       |

| 7.1.7. Outbound Post Queue                                 |       |

| 7.1.8. Inbound Free Queue                                  |       |

| 7.1.9. Outbound Free List FIFO                             |       |

| 7.1.10. I <sub>2</sub> O Enable Sequence                   | . 7-5 |

| 8. PCI Power Management                                    | 8-1   |

| 8.1. Overview                                              |       |

| 8.1.1. PCI Power Management Functional Description         |       |

| 8.1.2. 66 MHz PCI Clock D <sub>2</sub> Power State Support |       |

| 8.1.3. D <sub>3cold</sub> Power State Support              |       |

| 8.1.5. Non-D <sub>3cold</sub> Wake-Up Request Example      |       |

|                                                            |       |

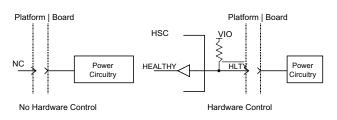

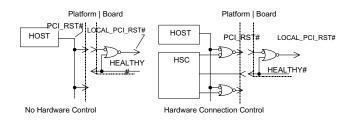

| 9. CompactPCI Hot Swap                                     | 9-1   |

| 9.1. Overview                                              |       |

| 9.1.1. Silicon Behavior during Initialization on PCI Bus   |       |

| 9.1.2. Configuration                                       |       |

| 9.2. Controlling Connection Processes                      |       |

| 9.2.1.1. Board Slot Control                                |       |

| 9.2.1.2. Board Healthy                                     |       |

| 9.2.1.3. Platform Reset                                    |       |

| 9.2.2. Software Connection Control                         |       |

| 9.2.2.1. Ejector Switch and Blue Status LED.               |       |

| 9.2.2.2. ENUM#                                             |       |

| 9.2.2.3. 64EN# (64-bit Enable)                             |       |

| 9.2.2.5. Hot Swap Capabilities Register                    |       |

| 10. PCI Vital Product Data (VPD)                           | 0-1   |

|                                                            | 40.4  |

| 10.1. Overview                                             |       |

| 10.2. VPD Capabilities Registers                           |       |

| 10.2.2. VPD Data Register                                  |       |

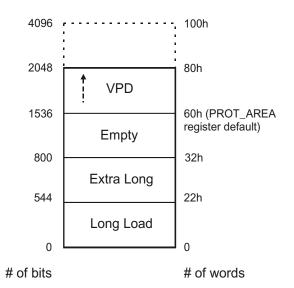

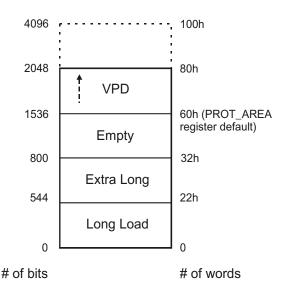

| 10.3. VPD Serial EEPROM Partitioning.                      |       |

| 10.4. Sequential Read-Only.                                | 10-2  |

| 10.5. Random Read and Write                                | 10-2  |

| 11. Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.1. Summary of Register Differences.       11-1         11.2. Register Address Mapping       11-3         11.3. PCI Configuration Registers       11-8         11.4. Local Configuration Registers       11-20         11.5. Runtime Registers       11-36         11.6. DMA Registers       11-43         11.7. Messaging Queue (I <sub>2</sub> O) Registers       11-53                                                                                                                                                         |

| 12. Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12.1. Pin Summary       12-1         12.2. Pull-Up and Pull-Down Resistors       12-1         12.3. Pinout Common to All Bus Modes       12-3         12.4. M Bus Mode Pinout       12-11         12.5. C Bus Mode Pinout       12-16         12.6. J Bus Mode Pinout       12-21         12.7. JTAG Interface       12-27         12.7.1. IEEE 1149.1 Test Access Port       12-27         12.7.2. JTAG Instructions       12-27         12.7.3. JTAG Boundary Scan       12-28         12.7.4. JTAG Reset Input TRST#       12-28 |

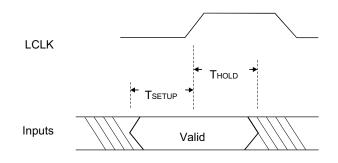

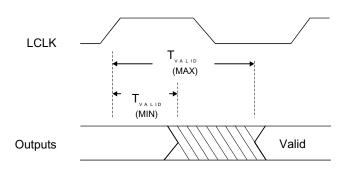

| 13. Electrical Specifications 13-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

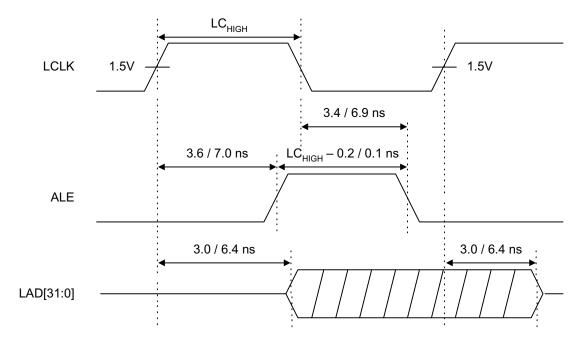

| 13.1. 3.3 and 5V Mixed-Voltage Devices and Power Sequence13-113.2. General Electrical Specifications13-213.3. Local Inputs13-513.4. Local Outputs13-713.5. ALE Output Delay Timing for All Local Bus Clock Rates13-9                                                                                                                                                                                                                                                                                                                |

| 14. Physical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

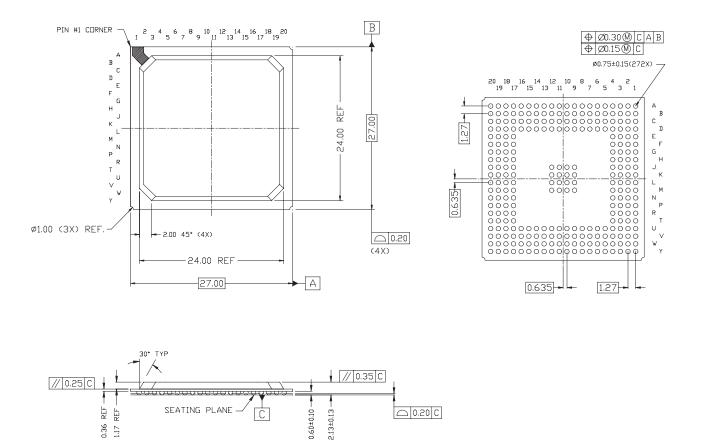

| 14.1. Mechanical Dimensions    14-1      14.2. Ball Grid Assignments    14-2                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A. General Information A-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A.1. Product Ordering Information       A-1         A.2. United States and International Representatives, and Distributors       A-2         A.3. Technical Support       A-2                                                                                                                                                                                                                                                                                                                                                       |

### FIGURES

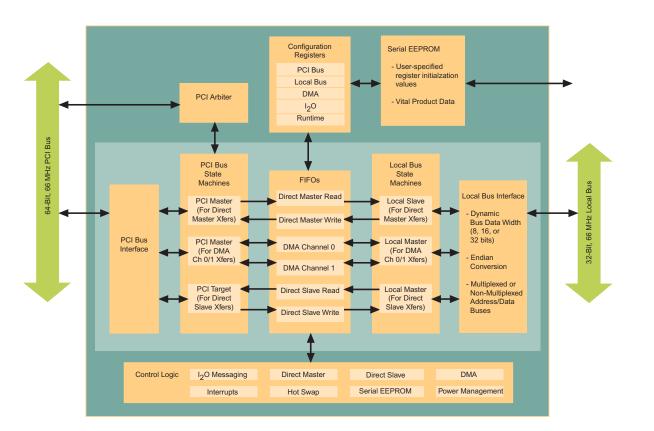

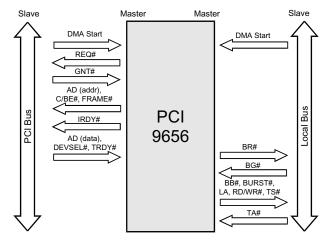

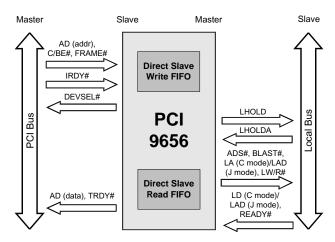

| PCI 9656 Block Diagramxxx                                                                                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

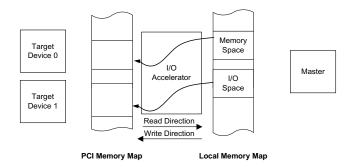

| 1-1. Direct Master Address Mapping1-2                                                                                                                     |

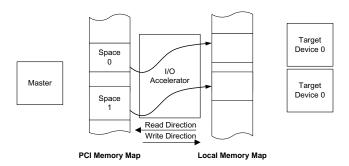

| 1-2. Direct Slave Address Mapping                                                                                                                         |

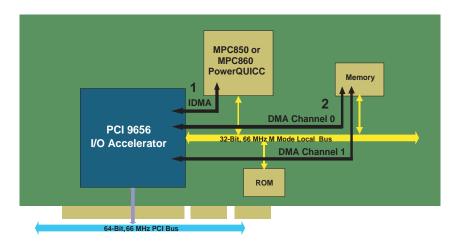

| 1-3. High-Performance MPC850 or MPC860 PowerQUICC Adapter Design                                                                                          |

| 1-4. PCI 9656 CompactPCI Peripheral Card                                                                                                                  |

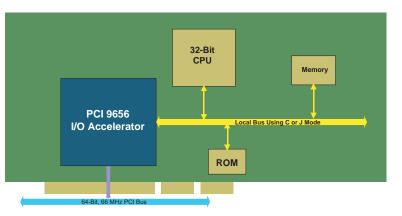

| 1-5. PCI 9656 PCI Adapter Card with C or J Mode Processor                                                                                                 |

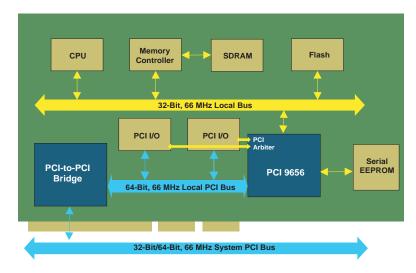

| 1-6. PCI 9656 PCI Adapter Card with Local PCI I/O and PCI-to-PCI Bridge                                                                                   |

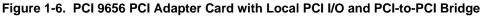

| 1-7. PCI 9656 Embedded Host System with Generic Host CPU                                                                                                  |

|                                                                                                                                                           |

| 2-1. Wait States                                                                                                                                          |

| 2-2. Serial EEPROM Memory Map2-10                                                                                                                         |

| 2-3. Serial EEPROM Timeline                                                                                                                               |

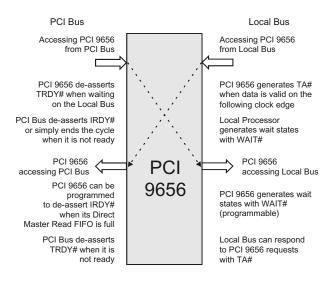

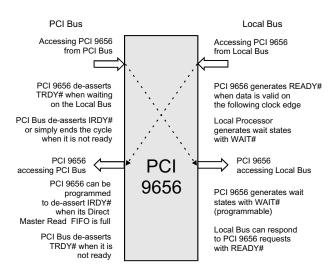

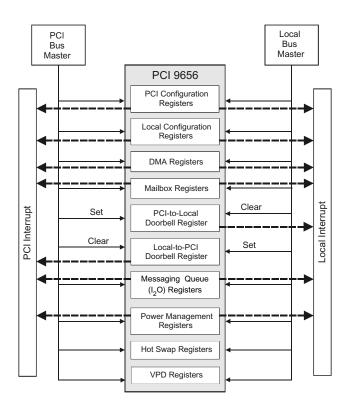

| 2-4. PCI 9656 Internal Register Access                                                                                                                    |

|                                                                                                                                                           |

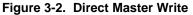

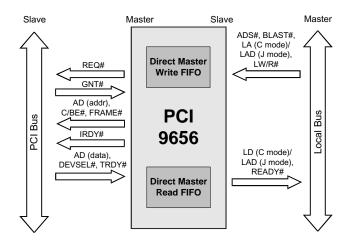

| 3-1. Direct Master Access to the PCI Bus                                                                                                                  |

| 3-2. Direct Master Write                                                                                                                                  |

| 3-3. Direct Master Read                                                                                                                                   |

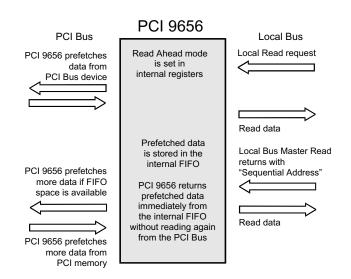

| 3-4. Direct Master Read Ahead Mode                                                                                                                        |

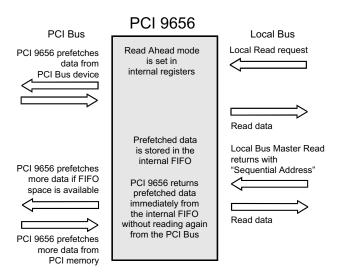

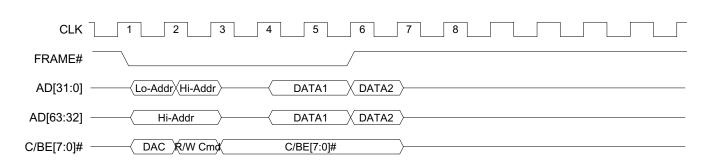

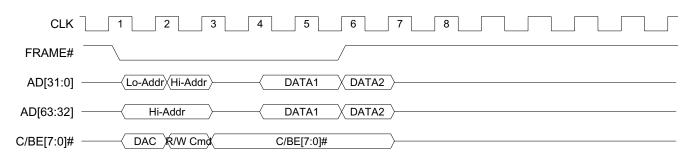

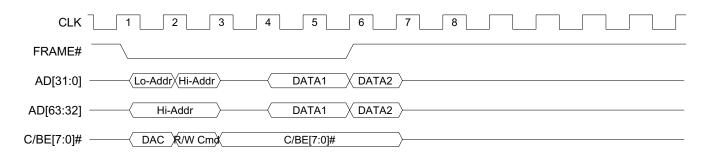

| 3-5. PCI Dual Address Cycle Timing                                                                                                                        |

| 3-6. Direct Slave Write                                                                                                                                   |

| 3-7. Direct Slave Read                                                                                                                                    |

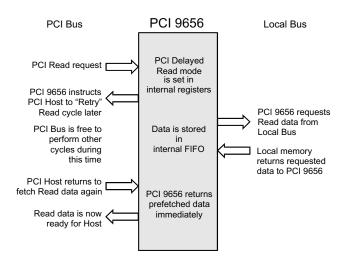

| 3-8. Direct Slave Delayed Read Mode                                                                                                                       |

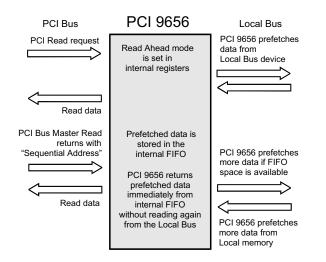

| 3-9. Direct Slave Read Ahead Mode                                                                                                                         |

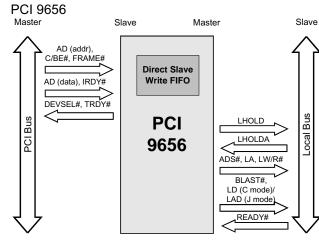

| 3-10. Local Bus Direct Slave Access                                                                                                                       |

| 3-11. PCI Dual Address Cycle Timing                                                                                                                       |

| 3-12. DMA Block Mode Initialization (Single Address or Dual Address PCI)                                                                                  |

| 3-13. DMA, PCI-to-Local Bus                                                                                                                               |

| 3-14. DMA, Local-to-PCI Bus                                                                                                                               |

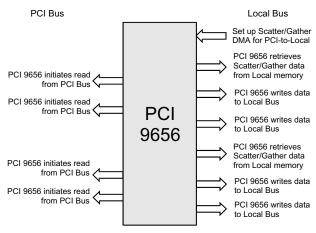

| 3-15. DMA Scatter/Gather Mode from PCI-to-Local Bus (Control Access from the Local Bus)                                                                   |

| 3-16. DMA Scatter/Gather Mode from Local-to-PCI Bus (Control Access from the PCI Bus)                                                                     |

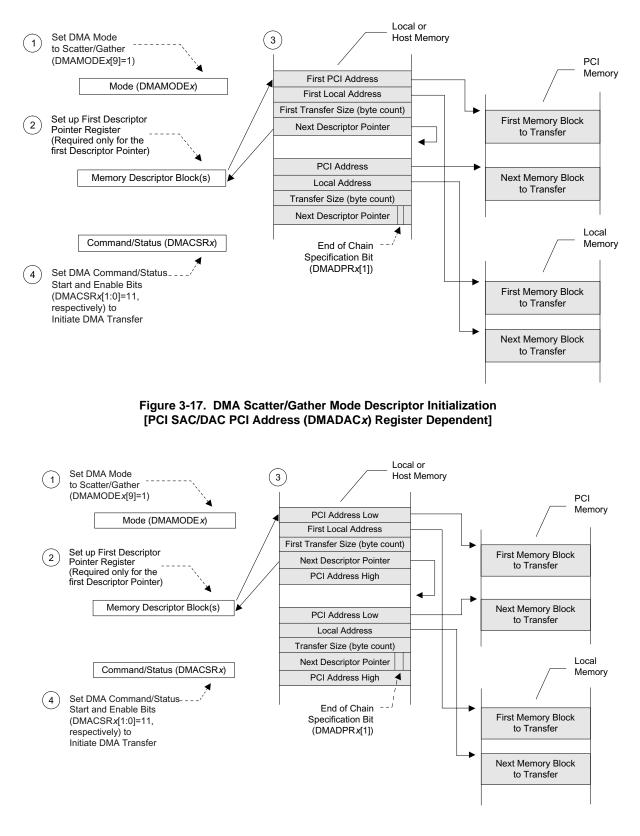

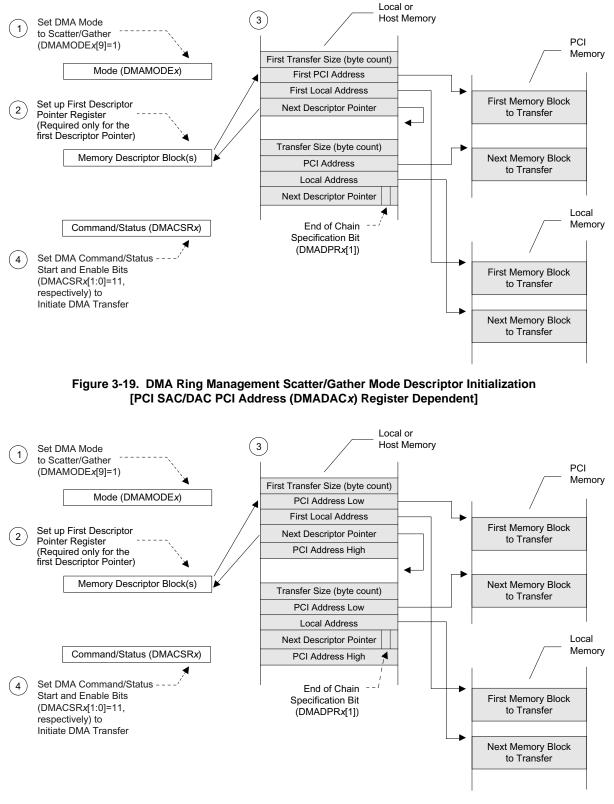

| 3-17. DMA Scatter/Gather Mode Descriptor Initialization                                                                                                   |

| [PCI SAC/DAC PCI Address (DMADACx) Register Dependent]                                                                                                    |

| 3-18. DMA Scatter/Gather Mode Descriptor Initialization<br>[DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)                  |

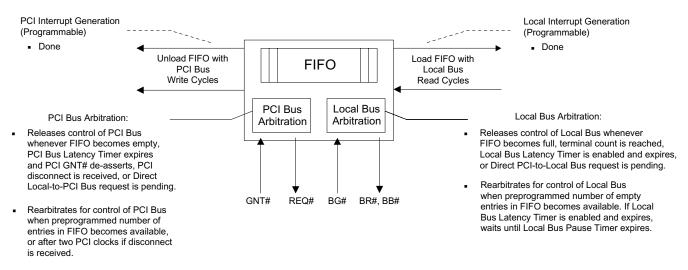

| 3-19. DMA Ring Management Scatter/Gather Mode Descriptor Initialization                                                                                   |

| [PCI SAC/DAC PCI Address (DMADACx) Register Dependent]                                                                                                    |

| 3-20. DMA Ring Management Scatter/Gather Mode Descriptor Initialization<br>[DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)] |

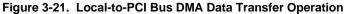

| 3-21. Local-to-PCI Bus DMA Data Transfer Operation                                                                                                        |

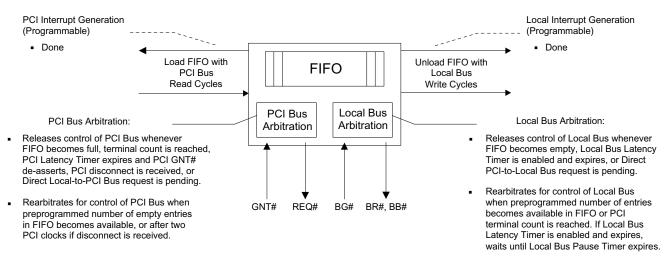

| 3-22. PCI-to-Local Bus DMA Data Transfer Operation                                                                                                        |

|                                                                                                                                                           |

| 4-1. Wait States                                                                                                                                          |

| 4-2. Serial EEPROM Memory Map4-12                                                                                                                         |

| 4-3. Serial EEPROM Timeline                                                                                                                               |

| 4-4. PCI 9656 Internal Register Access                                                                                                                    |

| 5-1. Direct Master Access of the PCI Bus5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-5                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 5-2. Direct Master Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-6                                                                                                                                    |

| 5-3. Direct Master Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-6                                                                                                                                    |

| 5-4. Direct Master Read Ahead Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-8                                                                                                                                    |

| 5-5. PCI Dual Address Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·11                                                                                                                                    |

| 5-6. Direct Slave Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ·15                                                                                                                                    |

| 5-7. Direct Slave Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ·16                                                                                                                                    |

| 5-8. Direct Slave Delayed Read Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ·16                                                                                                                                    |

| 5-9. Direct Slave Read Ahead Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ·17                                                                                                                                    |

| 5-10. Local Bus Direct Slave Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ·20                                                                                                                                    |

| 5-11. PCI Dual Address Cycle Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ·24                                                                                                                                    |

| 5-12. DMA Block Mode Initialization (Single Address or Dual Address PCI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -25                                                                                                                                    |

| 5-13. DMA, PCI-to-Local Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -25                                                                                                                                    |

| 5-14. DMA, Local-to-PCI Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -25                                                                                                                                    |

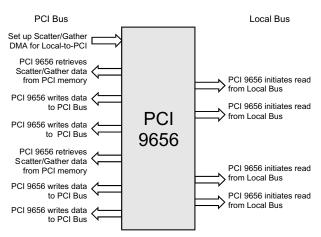

| 5-15. DMA Scatter/Gather Mode from PCI-to-Local Bus (Control Access from the Local Bus)5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -26                                                                                                                                    |

| 5-16. DMA Scatter/Gather Mode from Local-to-PCI Bus (Control Access from the PCI Bus)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -26                                                                                                                                    |

| 5-17. DMA Scatter/Gather Mode Descriptor Initialization<br>[PCI SAC/DAC PCI Address (DMADACx) Register Dependent]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ·28                                                                                                                                    |

| 5-18. DMA Scatter/Gather Mode Descriptor Initialization<br>[DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)] 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -28                                                                                                                                    |

| 5-19. DMA Ring Management Scatter/Gather Mode Descriptor Initialization<br>[PCI SAC/DAC PCI Address (DMADACx) Register Dependent]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -29                                                                                                                                    |

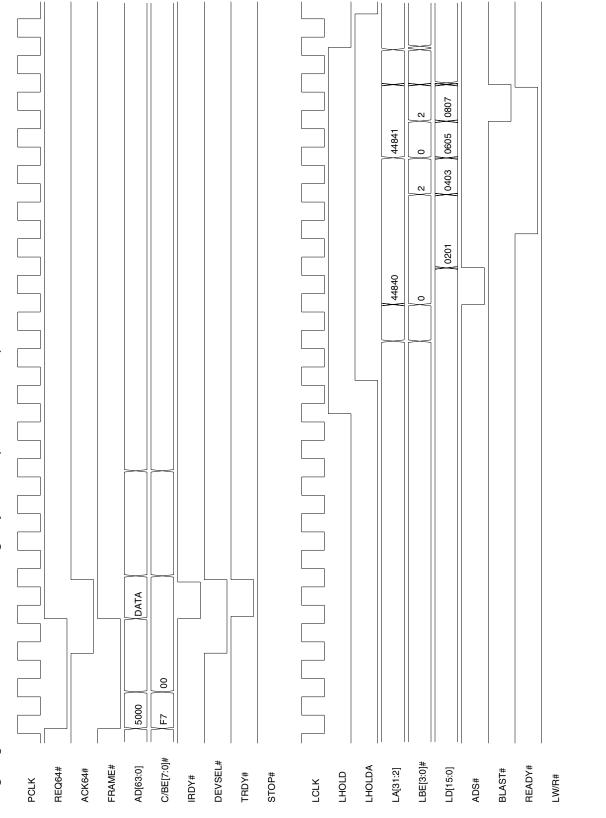

| 5-20. DMA Ring Management Scatter/Gather Mode Descriptor Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

| [DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)] 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ·29                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                        |

| [DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)]5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -32                                                                                                                                    |

| [DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)]5-2<br>5-21. Local-to-PCI Bus DMA Data Transfer Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -32<br>-32                                                                                                                             |

| [DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)]       5-21.         5-21. Local-to-PCI Bus DMA Data Transfer Operation       5-3         5-22. PCI-to-Local Bus DMA Data Transfer Operation       5-3         6-1. Interrupt and Error Sources       6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -32<br>-32<br>6-1                                                                                                                      |

| [DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)]5-2<br>5-21. Local-to-PCI Bus DMA Data Transfer Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -32<br>-32<br>6-1                                                                                                                      |

| [DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)]       5-21.         5-21. Local-to-PCI Bus DMA Data Transfer Operation       5-3         5-22. PCI-to-Local Bus DMA Data Transfer Operation       5-3         6-1. Interrupt and Error Sources       6         6-2. Mailbox and Doorbell Message Passing       6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -32<br>-32<br>6-1<br>6-3                                                                                                               |

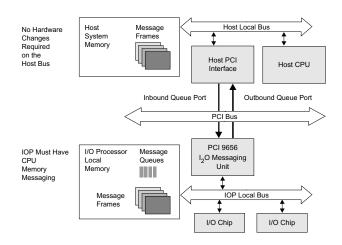

| [DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)]       5-21.         5-21. Local-to-PCI Bus DMA Data Transfer Operation       5-3         5-22. PCI-to-Local Bus DMA Data Transfer Operation       5-3         6-1. Interrupt and Error Sources       6         6-2. Mailbox and Doorbell Message Passing       6         7-1. Typical I <sub>2</sub> O Server/Adapter Card Design       7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -32<br>-32<br>6-1<br>6-3<br>7-1                                                                                                        |

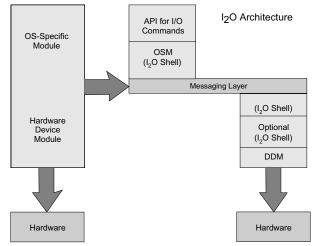

| [DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)]       5-21.         5-21. Local-to-PCI Bus DMA Data Transfer Operation       5-3         5-22. PCI-to-Local Bus DMA Data Transfer Operation       5-3         6-1. Interrupt and Error Sources       6         6-2. Mailbox and Doorbell Message Passing       6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -32<br>-32<br>6-1<br>6-3<br>7-1<br>7-1                                                                                                 |

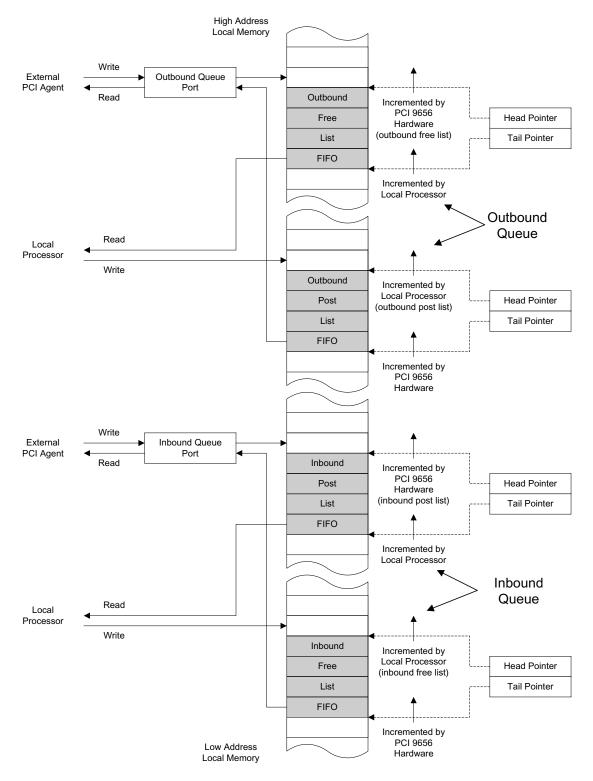

| [DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)]       5-21.         5-21. Local-to-PCI Bus DMA Data Transfer Operation       5-3         5-22. PCI-to-Local Bus DMA Data Transfer Operation       5-3         6-1. Interrupt and Error Sources       6         6-2. Mailbox and Doorbell Message Passing       6         7-1. Typical I <sub>2</sub> O Server/Adapter Card Design       7         7-2. Driver Architecture Compared       7         7-3. Circular FIFO Operation       7                                                                                                                                                                                                                                                                                                                                                                                           | -32<br>-32<br>6-1<br>6-3<br>7-1<br>7-1<br>7-4                                                                                          |

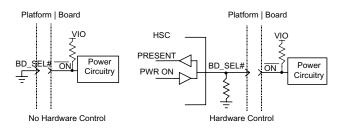

| [DAC PCI Address (DMAMODEx[18]) Descriptor Dependent (PCI Address High Added)]       5-21.         5-21. Local-to-PCI Bus DMA Data Transfer Operation       5-3         5-22. PCI-to-Local Bus DMA Data Transfer Operation       5-3         6-1. Interrupt and Error Sources       6         6-2. Mailbox and Doorbell Message Passing       6         7-1. Typical I <sub>2</sub> O Server/Adapter Card Design       7         7-2. Driver Architecture Compared       7         7-3. Circular FIFO Operation       7         9-1. Redirection of BD_SEL#       9                                                                                                                                                                                                                                                                                                                                               | -32<br>-32<br>6-1<br>6-3<br>7-1<br>7-1<br>7-4<br>9-2                                                                                   |